# CMS80F231x 用户手册

增强型闪存 8 位 1T 8051 单片机

Rev. 1.1.7

### 请注意以下有关CMS知识产权政策

\*中微半导体(深圳)股份有限公司(以下简称本公司)已申请了专利,享有绝对的合法权益。与本公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害本公司专利权的公司、组织或个人,本公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨本公司因侵权行为所受的损失、或侵权者所得的不法利益。

\*中微半导体(深圳)股份有限公司的名称和标识都是本公司的注册商标。

\*\*本公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。然而本公司对于规格内容的使用不负责任。文中提到的应用其目的仅仅是用来做说明,本公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。本公司的产品不授权适用于救生、维生器件或系统中作为关键器件。本公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考官方网站 www.mcu.com.cn

# 目录

| 1.1 功能特性 1.2 系統体特極圏 1.3 管脚分布 1.3.1 CMS0F2313 引脚圏 1.3.2 CMS0F2313 引脚圏 1.3.3 CMS0F2317 引脚圏 1.1.3 管脚分布 1.3.1 不然知るF存置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1. | 产品    | <b></b>              | 9    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|----------------------|------|

| 1.3 管脚分布 1.3.1 CMS80F2313 引脚图 11 1.3.2 CMS80F2316 引脚图 11 1.3.3 CMS80F2317 引脚图 11 1.3.4 系統配置寄存器 11 1.5 在线車行線程 16 1.6 在线車付線程 16 1.6 在线車付線程 17 2.1 存储器 15 2.1 存储器 15 2.1.1 程序存储器 16 2.1.1 程序存储器 15 2.1.1 程序存储器 15 2.1.1 程序存储器 15 2.1.1 被序存储器 15 2.1.2 复位向量 (COOOOH) 2 2.1.3 数据存储器 (IRAM) 2 2.1.4 特殊功能寄存器表 (SFR) 2 2.1.5 外部数据存储器 (IRAM) 2 2.1.5 外部数据存储器 (IRAM) 2 2.1.6 特殊功能寄存器表 (XSFR) 2 2.1.6 特殊功能寄存器表 (XSFR) 2 2.1.7 対象数据存储器 (IRAM) 2 2.1.8 財務対能符音器表 (XSFR) 3 2.1 存储器 (IRAM) 3 2.1 全                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 1.1   | 功能特性                 | (    |

| 1.3.1 CMS80F2313 引脚图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 1.2   | 系统结构框图               | 11   |

| 1.3.2 CMS80F2316 引脚图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 1.3   | 管脚分布                 | 12   |

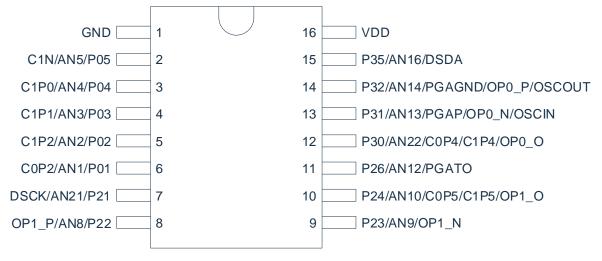

| 1.3.3 CMS80F2317 引脚图 15 1.4 系统配置寄存器 16 1.5 在线串行编程 16 1.6 在线调试模式 16 1.6 在线调试模式 17 2. 中央处理器 (CPU) 15 2.1 存储器 15 2.1.1 程序存储器 15 2.1.2 复位向量(0000H) 27 2.1.3 数据存储器 (IRAM) 27 2.1.3 数据存储器 (IRAM) 27 2.1.4 特殊功能寄存器表 (SPR) 26 2.1.5 外部数据存储器 (XRAM) 27 2.1.6 特殊功能寄存器表 (SPR) 27 2.1.6 特殊功能寄存器表 (XSFR) 27 2.1.7 理核助能寄存器表 (XSFR) 27 2.1.8 財務分析器 (DPTRO/DPTR1) 37 2.1.9 数据指计选择等存器 (DPTRO/DPTR1) 37 2.1.0 数据指计选择等存器 (DPTRO/DPTR1) 37 2.1.1 时报的寄存器 (MTA) 38 2.1.1 可用的转数 (MTA) 38 2.1.1 功能控制寄存器 (CDRO) 38 2.1.1 功能控制寄存器 (CDRO) 38 2.1.1 功能控制寄存器 (MTA) 38 2.1.1 示统振荡器 37 3.1 系统振荡器 37 3.1 系统振荡器 37 3.1 系统时钟结构 38 3.2 复位时间 38 3.2 复位时间 36 3.3 可伸结构 38 3.2 复位时间 36 3.3 可伸结构 38 3.3 可伸结构 38 3.3 可能结构 38 3.3 可能的 38 3.3 |    | 1.3.1 | CMS80F2313 引脚图       | 12   |

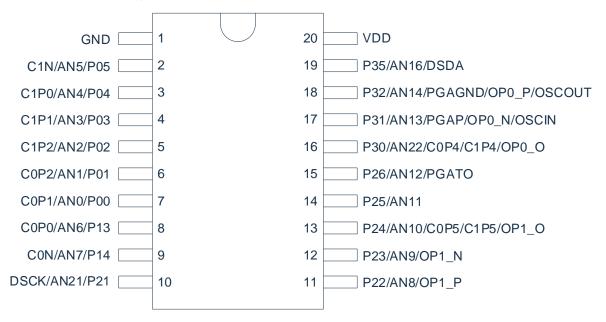

| 1.4 系統配置寄存器 16 1.5 在线串行練程 18 1.6 在线明试模式 16 1.6 在线明试模式 16 1.6 在线明试模式 17 2. 中央处理器 (CPU) 15 2.1 存储器 15 2.1.1 程序存储器 15 2.1.1 程序存储器 15 2.1.2 复位向量 (0000H) 27 2.1.3 数据存储器 (IRAM) 27 2.1.4 特殊功能寄存器核 (SFR) 27 2.1.5 外部数据存储器 (XRAM) 27 2.1.6 特殊功能寄存器核 (XSFR) 27 2.1.5 外部数据存储器 (XSFR) 27 2.2 累加器 (ACC) 31 2.3 B寄存器 (B) 31 2.4 堆栈指针寄存器 (SP) 31 2.4 堆栈指针寄存器 (DPTR///DPTR/) 31 2.6 数据指针选择寄存器 (DPTR///DPTR/) 31 2.6 数据指针选择寄存器 (DPS) 31 2.7 程序状态寄存器 (PSW) 32 2.8 程序计数器 (PC) 33 2.7 程序状态寄存器 (PSW) 33 2.10 看门询计数器 (WDT) 33 2.10 相门划计数器 (WDT) 33 2.10 相门划计数器 (WDT) 33 2.10 相门划计数器 (WDT) 33 2.10 数据 计划计数器 (WDT) 33 2.11 功能控制寄存器 (MDCOM) 34 2.10.3 WDT 溢出周期 35 2.10.3 WDT 溢出周期 37 2.10.3 WDT 溢出周期 37 2.10.3 WDT 溢出控制寄存器 (MCOM) 36 2.11 功能控制寄存器 (CKOM) 37 3.1 系统时钟结构 37 3.1 系统时钟结构 37 3.1 系统服荡器 37 3.2 复位时间 37 3.3 系统时钟结构 37 3.3 环线矩钟结构 37 3.3 环线矩钟结构 37 3.3 环线矩钟结构 37 3.3 系统矩钟结构 37 3.3 环线矩钟结构 37 3.4 环纸压度位 44 4.4 上电复位 44 4.4 上电复位 44 4.1 LR 低压复位 44 4.3 LR 低压复位 44 4.4 Three Country 44 4.4 Three Country 46 4.4 Three Country 47 4.5 Three Country  |    | 1.3.2 | CMS80F2316 引脚图       | 12   |

| 1.5 在线串行編程 16 在线调记模式 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 1.3.3 | CMS80F2317 引脚图       | 13   |

| 1.6 在线调试模式       16         2. 中央处理器(CPU)       15         2.1 存储器       15         2.1.1 程序存储器       15         2.1.2 复位向量(0000H)       22         2.1.3 数据存储器(IRAM)       22         2.1.4 特殊功能寄存器表(SFR)       22         2.1.5 外部数据存储器(XRAM)       2         2.1.6 特殊功能寄存器表(XSFR)       22         2.1.6 特殊功能寄存器表(XSFR)       22         2.2 累加器(ACC)       33         2.3 B寄存器(BD       35         2.4 堆栈指针寄存器(SP)       36         2.5 数据指针寄存器(OPS)       37         2.6 数据针选择等存器(OPS)       36         2.7 程序状态寄存器(PSW)       36         2.8 程序计数器(PCO       35         2.9 时序存取寄存器(TA)       36         2.10 都门并数器(WDT)       36         2.10 WDT 溢出周期       3-         2.10 WDT 溢出局期       3-         2.10 WDT 溢出房間等所(FUNCCR)       36         3. 系统时钟       37         3.1 系统服務器       33         3.2 复位时间       33         3.3 原務的時結构       36         3.3.1 系统服務器       33         3.2 原務認時結构       36         3.3.2 振荡器控制寄存器CLKDIV       36         3.3.3 原務控制寄存器CLKDIV       36 <t< td=""><td></td><td>1.4</td><td>系统配置寄存器</td><td> 16</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 1.4   | 系统配置寄存器              | 16   |

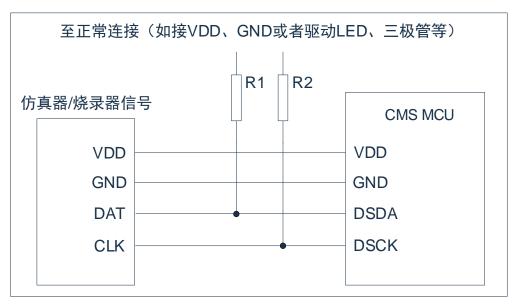

| 2. 中央处理器(CPU)       15         2.1 存储器       15         2.1.1 程序存储器       15         2.1.2 复位向量(0000H)       22         2.1.3 数据存储器(IRAM)       22         2.1.4 特殊功能寄存器表(SFR)       22         2.1.5 外部数据存储器(KRAM)       22         2.1.6 特殊功能寄存器表(XSFR)       26         2.2 累加器(ACC)       32         2.3 B 寄存器(B)       35         2.4 埋栈指计寄存器(SP)       36         2.5 数据指针选择寄存器(DPTR0/DPTR1)       36         2.6 数据指针选择寄存器(PSW)       36         2.7 程序状态寄存器(PSW)       36         2.8 程序计数器(PCO       33         2.9 时序存取寄存器(TA)       30         2.10.1 WDT溢出周期       34         2.10.2 有门狗控制寄存器(CKCON       36         2.11 功能控制寄存器(FUNCCR)       36         3. 系統时钟       37         3.1 系统振荡器       37         3.2 复位时间       36         3.3.1 系统振钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能対转构       36         3.3.3 死统时钟结构       36         3.3.3 水线振荡器控制寄存器 CLKDIV       36         3.3.3 水线振荡器控制寄存器 CLKDIV       36         3.3.3 水线振荡器控制寄存器 CLKDIV       36         3.3.3 水线振荡器控制寄存器 CLKDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 1.5   | 在线串行编程               | 18   |

| 2.1 存储器       15         2.1.1 程序存储器       15         2.1.2 复位向置(0000H)       22         2.1.3 数据存储器(IRAM)       22         2.1.4 特殊功能寄存器表(SFR)       22         2.1.5 外部数据存储器(IRAM)       22         2.1.6 特殊功能寄存器表(XSFR)       22         2.2 累加器(ACC)       33         2.3 B寄存器(BD       33         2.4 堆栈封针寄存器(DPTR0/DPTR1)       35         2.5 数据拍针竞存器(DPS)       35         2.7 程序状态寄存器(PSW)       36         2.8 程序计数器(PC)       33         2.9 时序存取寄存器(TA)       36         2.10.1 WDT进出周期       36         2.10.2 看门狗往刺寄存器(WDCON       36         2.10.3 WDT溢出控制寄存器(CKCON       36         2.11 功能控制寄存器(FUNCCR)       36         3.3 系统时钟       37         3.3 系统时钟结构       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器(CKCON       36         3.3.3 功能控制寄存器(CKCON       36         3.3.1 系统时钟结构       36         3.3.2 排荡器控制寄存器(CKCON       36         3.3.3 功能的特结构       36         3.3.3 功能的特结构       36         3.3.3 功能的特结构       36         3.3.3 功能控制       4       2位         4.1 上电复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 1.6   | 在线调试模式               | 18   |

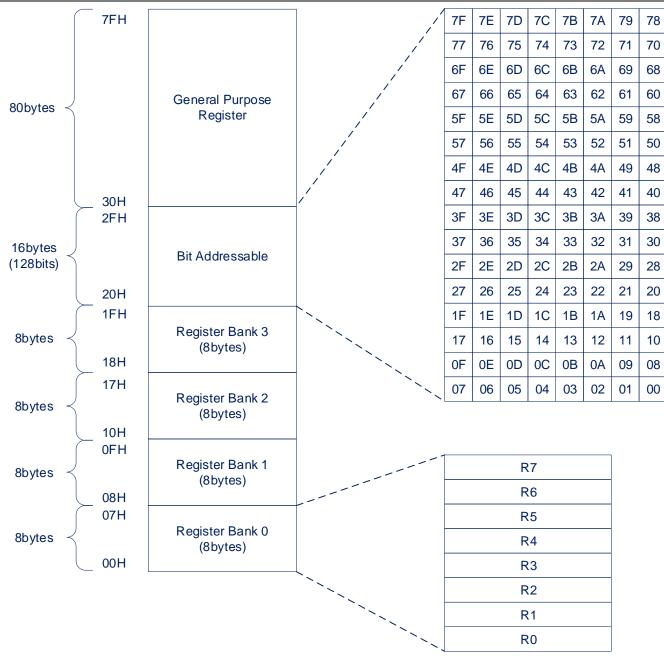

| 2.1.1 程序存储器       15         2.1.2 复位向量(0000H)       21         2.1.3 数据存储器(KRAM)       22         2.1.4 特殊功能寄存器表(SFR)       22         2.1.5 外部数据存储器(XRAM)       22         2.1.6 特殊功能寄存器表(XSFR)       25         2.2 累加器(ACC)       31         2.3 B 寄存器(B)       31         2.4 堆栈拍针寄存器(SP)       31         2.5 数据拍针寄存器(DPRO/DPTR1)       33         2.6 数据拍计选择寄存器(DPS)       31         2.7 程序状态寄存器(PSW)       32         2.8 程序计数器(PC)       33         2.9 时序存储器(WDT)       33         2.10 看 (別計 数器(WDT)       34         2.10.1 WDT 溢出周期       34         2.10.2 看 (別計費務保 WDCON)       36         2.11 功能控制寄存器(FUNCCR)       36         3. 系統的如       36         3.3.1 系統開清器       37         3.3.2 复位时间       33         3.3.3 功能时執检查       36         3.3.1 系统即转和参存器 CLKDIV       36         3.3.2 振荡健康检测寄存器 CLKDIV       36         3.3.3 功能时執控制寄存器 CLKDIV       36         3.3.3 功能时转和参存器 CLKDIV       36         4. 复位       46         4.1 上电复位       46         4.2 外部复位       47         4.3 LVR低度量位       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2. | 中央    | ·处理器(CPU)            | . 19 |

| 2.1.1 程序存储器       15         2.1.2 复位向量(0000H)       2         2.1.3 数据存储器(KRAM)       2         2.1.4 特殊功能寄存器表(SFR)       20         2.1.5 外部数据存储器(XRAM)       2         2.1.6 特殊功能寄存器表(XSFR)       22         2.2 累加器(ACC)       3         2.3 B 寄存器(B)       3         2.4 堆栈射守存器(SP)       3         2.5 数据指针寄存器(CPS)       3         2.6 数据指计选择寄存器(DPS)       3         2.7 程序状态寄存器(PSW)       3         2.8 程序计数器(PC)       3         2.9 时序存储器(CPD)       3         2.10 相介射计数器(WDT)       3         2.10.1 WDT 溢出周期       3         2.10.2 看了新建制寄存器(WDCON       3         2.11 功能控制寄存器(FUNCCR)       3         3. 系统时钟       3         3.1 系统振荡器       3         3.2 复位时间       3         3.3.1 系统即转转       3         3.3.2 振荡器控制寄存器 CLKDIV       3         3.3.3 功能时钟控制寄存器 CLKDIV       3         3.3.3 功能时钟控制寄存器 CLKON       3         4. 复位       4         4.1 上电复位       4         4.2 外部复位       4         4.3 LVR低压复位       4         4.4 看几为复位(WDT)       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 21    | 存储器                  | 19   |

| 2.1.2 复位向量(0000H)       2.         2.1.3 数据存储器(IRAM)       2.         2.1.4 特殊功能寄存储表(SFR)       2.         2.1.5 外部数据存储器(XRAM)       2.         2.1.6 特殊功能寄存储表(XRSFR)       2.         2.2 累加器(ACC)       3.         2.3 B 有存器(B)       3.         2.4 堆栈指针寄存器(SP)       3.         2.5 数据指针寄存器(DPRO/DPTR1)       3.         2.6 数据针选择寄存器(DPS)       3.         2.7 程序状态寄存器(PSW)       3.         2.8 程序计数器(PC)       33         2.9 时序存取寄存器(TA)       33         2.10.1 WDT 溢出周期       34         2.10.2 看门狗控制寄存器(WDCON       36         2.10.3 WDT 溢出控制寄存器(CKCON       36         2.11 功能控制寄存器(FUNCCR)       36         3. 系统时钟       37         3.1 系统据清器       33         3.2 复位时间       33         3.3.1 系统时钟结构       36         3.2.2 振荡器控制寄存器(CKCON       36         4. 复位       4         4.1 上电复位       4         4.2 外部复位       44         4.3 LVR低质复位       44         4.4 看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |                      |      |

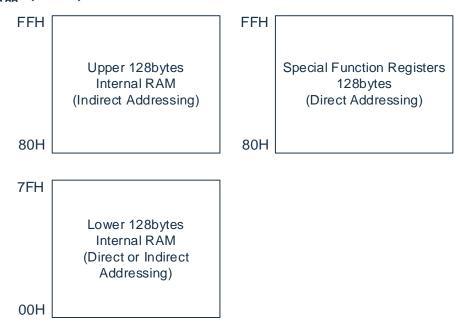

| 2.1.3       数据存储器(IRAM)       2.         2.1.4       特殊功能寄存器表(SFR)       2.         2.1.5       外部数据存储器(KRAM)       2.         2.1.6       特殊功能寄存器表(XSFR)       2.         2.2       累加器(ACC)       3.         2.3       B 奇存器(B)       3.         2.4       堆栈指针寄存器(DPTRO/DPTR1)       3.         2.6       数据针选择寄存器(DPTRO/DPTR1)       3.         2.6       数据针选择寄存器(DPSD)       3.         2.7       程序状态寄存器(PSW)       3.         2.8       程序计数器(PCD)       3.         2.9       时序存服寄存器(TA)       3.         2.10       看门狗针数器(WDT)       3.         2.10.1       WDT 溢出周期       3.         2.10.2       看门狗村會寄務 WDCON       3.         2.10.3       WDT 溢出周期       3.         2.10.1       功能控制寄存器(FUNCCR)       3.         3.       系统时钟       3.         3.1       系统振荡器       3.         3.2       复位时间       3.         3.3.1       系统时钟结构       3.         3.3.2       振荡器性制等存器 CLKDIV       3.         3.3.3       功能时转控制等存器 CLKDIV       3.         3.3.3       功能时转控制等存器 CLKDIV       3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       |                      |      |

| 2.1.4 特殊功能寄存器表(XRAM)       26         2.1.5 外部数据存储器(XRAM)       26         2.1.6 特殊功能寄存器表(XSFR)       21         2.2 累加器(ACC)       33         2.3 B 寄存器(BB       33         2.4 堆栈指针寄存器(DPTRO/DPTR1)       35         2.5 数据指针选择寄存器(DPS)       35         2.7 程序状态寄存器(PSW)       36         2.8 程序计数器(PCO       36         2.9 时序存取寄存器(TA)       36         2.10 看门狗计数器(WDT)       36         2.10.2 看门沟柱制寄存器 WDCON       36         2.10.3 WDT 溢出控制寄存器 WDCON       36         2.10.3 WDT 溢出控制寄存器 CKCON       36         2.11 功能控制寄存器(FUNCCR)       36         3.3 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       36         3.3.1 系统时转结构       36         3.2.2 振荡器控制寄存器 CLKDIV       36         3.3.3 成時转控制寄存器 CLKDIV       36         3.3.3 功能时转控制寄存器 CLKON       36         4.1 上电复位       46         4.2 外部复位       46         4.3 LVR 低压复位       46         4.4 看门狗复位(WDT)       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.1.3 |                      |      |

| 2.1.5 外部数据存储器(XRAM)       2.2         2.1.6 特殊功能寄存器表(XSFR)       26         2.2 累加器(ACC)       3         2.3 B 寄存器(B)       3         2.4 堆栈指针寄存器(SP)       3         2.5 数据指针选择寄存器(DPTR//DPTR1)       3         2.6 数据指针选择寄存器(DPS)       3         2.7 程序状态寄存器(PSW)       3         2.8 程序计数器(PC)       3         2.9 时序存取奇存器(TA)       3         2.10 看门狗针数器(WDT)       3         2.10.2 看门狗控制寄存器 CKCON       3         2.10.3 WDT 溢出控制寄存器 CKCON       3         2.11 功能控制寄存器(FUNCCR)       3         3. 系统时钟结构       3         3.1 系统服荡器       3         3.2 复位时间       3         3.3.1 系统时钟结构       3         3.3.2 振荡器控制寄存器 CKCON       3         3.3.3 功能时钟控制寄存器 CKCON       3         3.3.3 功能时钟控制寄存器 CKCON       3         3.3.1 系统时钟结构       3         3.3.2 扩张的转结构       3         3.3.3 功能时钟控制寄存器 CKCON       3         4. 复位       4         4.1 上电复位       4         4.2 外部复位       4         4.3 LVR 低压复位       4         4.4 看门物复位(WDT)       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       |                      |      |

| 2.2 累加器 (ACC)       33         2.3 B 寄存器 (B)       33         2.4 堆栈指针寄存器 (SP)       35         2.5 数据指针寄存器 (OPTRO/DPTR1)       35         2.6 数据指计选择寄存器 (DPS)       37         2.7 程序状态寄存器 (PSW)       32         2.8 程序计数器 (PC)       33         2.9 时序存取寄存器 (TA)       33         2.10 看门狗计数器 (WDT)       34         2.10.1 WDT 溢出周期       36         2.10.3 WDT 溢出控制寄存器 WDCON       36         2.11 功能控制寄存器 (FUNCCR)       36         3. 系统时钟       36         3.1 系统振荡器       36         3.2 复位时间       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CLKON       36         4. 复位       40         4.7 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位 (WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 2.1.5 | 外部数据存储器(XRAM)        | 24   |

| 2.3       B 寄存器 (B)       33         2.4       堆栈指针寄存器 (SP)       33         2.5       数据指针寄存器 (DPTR0/DPTR1)       35         2.6       数据指针选择寄存器 (DPS)       35         2.7       程序状态寄存器 (PSW)       36         2.8       程序计数器 (PC)       33         2.9       时序存取寄存器 (TA)       33         2.10       看门狗許数器 (WDT)       36         2.10.1       WDT 溢出周期       34         2.10.2       看门狗控制寄存器 WDCON       36         2.11       功能控制寄存器 (FUNCCR)       36         3. 系統时钟       37         3.1       系统振荡器       37         3.2       复位时间       36         3.3.1       系统时钟结构       36         3.3.1       系统时钟结构       36         3.3.2       振荡器控制寄存器 CLKDIV       36         3.3.3       功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门夠复位 (WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 2.1.6 | 特殊功能寄存器表(XSFR)       | 25   |

| 2.4 堆栈指针寄存器(SP)       33         2.5 数据指针寄存器(DPTR0/DPTR1)       33         2.6 数据指针选择寄存器(DPS)       35         2.7 程序状态寄存器(PSW)       32         2.8 程序计数器(PCD)       35         2.9 时序存取寄存器(TA)       35         2.10 看门狗许数器(WDT)       36         2.10.1 WDT溢出周期       36         2.10.2 看门狗诈控制寄存器 WDCON       36         2.11 功能控制寄存器(FUNCCR)       36         3. 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       36         3.3 时钟结构       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 2.2   | 累加器(ACC)             | 31   |

| 2.5       数据指针资存器(DPTRO/DPTR1)       3°         2.6       数据指针选择寄存器(DPS)       3°         2.7       程序状态寄存器(PSW)       3°         2.8       程序计数器(PC)       3°         2.9       时序存取寄存器(TA)       3°         2.10       看门狗拉制数器(WDT)       3°         2.10.1       WDT 溢出周期       3°         2.10.2       看门狗控制寄存器 WDCON       3°         2.10.3       WDT 溢出控制寄存器 CKCON       3°         2.11       功能控制寄存器 (FUNCCR)       3°         3.       系统时钟       3°         3.1       系统振荡器       3°         3.2       复位时间       3°         3.3       时结构       3°         3.3.1       系统时钟结构       3°         3.3.2       振荡器控制寄存器 CLKDIV       3°         3.3.3       功能钟转刺奇存器 CKCON       3°         4.       复位       4°         4.1       上电复位       4°         4.2       外部复位       4°         4.4       看门狗复位(WDT)       4°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 2.3   | B 寄存器(B)             | 31   |

| 2.6       数据指针选择寄存器(PPS)       33         2.7       程序状态寄存器(PSW)       32         2.8       程序计数器(PC)       33         2.9       时序存取寄存器(TA)       36         2.10       看门狗计数器(WDT)       34         2.10.2       看门狗控制寄存器 WDCON.       36         2.10.3       WDT 溢出控制寄存器 CKCON       36         2.11       功能控制寄存器 (FUNCCR)       36         3. 系统时钟       37         3.1       系统振荡器       37         3.2       复位时间       36         3.3.1       系统时钟结构       36         3.3.2       振荡器控制寄存器 CLKDIV       36         3.3.3       功能钟转刺寄存器 CKCON       35         4. 复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 2.4   | 堆栈指针寄存器(SP)          | 31   |

| 2.7       程序状态寄存器(PSW)       33         2.8       程序计数器(PC)       33         2.9       时序存取寄存器(TA)       35         2.10       看门狗计数器(WDT)       36         2.10.1       WDT 溢出周期       36         2.10.2       看门狗控制寄存器 WDCON       36         2.11       功能控制寄存器 CKCON       36         3.1       系统振荡器       37         3.2       复位时间       37         3.3       时钟结构       36         3.3.1       系统时钟结构       36         3.3.2       振荡器控制寄存器 CLKDIV       36         3.3.3       功能时钟控制寄存器 CKCON       36         4.1       上电复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 2.5   | 数据指针寄存器(DPTR0/DPTR1) | 31   |

| 2.8       程序计数器(PC)       33         2.9       时序存取寄存器(TA)       33         2.10       看门狗计数器(WDT)       34         2.10.1       WDT 溢出周期       34         2.10.2       看门狗控制寄存器 WDCON       36         2.11       功能控制寄存器 (FUNCCR)       36         3.       系统时钟       37         3.1       系统振荡器       37         3.2       复位时间       37         3.3.1       系统时钟结构       36         3.3.2       振荡器控制寄存器 CLKDIV       36         3.3.3       功能时钟控制寄存器 CKCON       36         4.       复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 2.6   | 数据指针选择寄存器(DPS)       | 31   |

| 2.9       时序存取寄存器(TA)       33         2.10       看门狗计数器(WDT)       34         2.10.1       WDT 溢出周期       36         2.10.2       看门狗控制寄存器 WDCON       36         2.10.3       WDT 溢出控制寄存器 CKCON       36         2.11       功能控制寄存器(FUNCCR)       36         3.       系统时钟       37         3.1       系统振荡器       37         3.2       复位时间       36         3.3.1       系统时钟结构       36         3.3.2       振荡器控制寄存器 CLKDIV       36         3.3.3       功能时钟控制寄存器 CKCON       36         4.       复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.7   | 程序状态寄存器(PSW)         | 32   |

| 2.10 看门狗计数器(WDT)       34         2.10.1 WDT 溢出周期       34         2.10.2 看门狗控制寄存器 WDCON       34         2.10.3 WDT 溢出控制寄存器 CKCON       35         2.11 功能控制寄存器(FUNCCR)       36         3. 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       37         3.3 时钟结构       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 2.8   | 程序计数器(PC)            | 33   |

| 2.10.1 WDT 溢出周期       3-4         2.10.2 看门狗控制寄存器 WDCON       3-6         2.10.3 WDT 溢出控制寄存器 CKCON       3-6         2.11 功能控制寄存器 (FUNCCR)       3-6         3. 系统时钟       3-7         3.1 系统振荡器       3-7         3.2 复位时间       3-7         3.3 时钟结构       3-6         3.3.1 系统时钟结构       3-6         3.3.2 振荡器控制寄存器 CLKDIV       3-7         3.3.3 功能时钟控制寄存器 CKCON       3-7         4. 复位       4-7         4.1 上电复位       4-7         4.2 外部复位       4-7         4.3 LVR 低压复位       4-7         4.4 看门狗复位(WDT)       4-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 2.9   | 时序存取寄存器(TA)          | 33   |

| 2.10.2 看门狗控制寄存器 WDCON.       34         2.10.3 WDT 溢出控制寄存器 CKCON.       36         2.11 功能控制寄存器 (FUNCCR).       36         3. 系统时钟.       37         3.1 系统振荡器.       37         3.2 复位时间.       37         3.3 时钟结构.       36         3.3.1 系统时钟结构.       36         3.3.2 振荡器控制寄存器 CLKDIV.       36         3.3.3 功能时钟控制寄存器 CKCON.       36         4. 复位.       40         4.1 上电复位.       40         4.2 外部复位.       42         4.3 LVR 低压复位.       42         4.4 看门狗复位 (WDT).       42         4.4 看门狗复位 (WDT).       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 2.10  | 看门狗计数器(WDT)          | 34   |

| 2.10.3 WDT 溢出控制寄存器 CKCON       36         2.11 功能控制寄存器 (FUNCCR)       36         3. 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       36         3.3 时钟结构       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 2.10. | 1 WDT 溢出周期           | 34   |

| 2.11 功能控制寄存器(FUNCCR)       36         3. 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       37         3.3 时钟结构       36         3.3.1 系统时钟结构       36         3.3.2 振荡器控制寄存器 CLKDIV       36         3.3.3 功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |                      |      |

| 3. 系统时钟       37         3.1 系统振荡器       37         3.2 复位时间       37         3.3 时钟结构       38         3.3.1 系统时钟结构       38         3.3.2 振荡器控制寄存器 CLKDIV       39         3.3.3 功能时钟控制寄存器 CKCON       39         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |                      |      |

| 3.1 系统振荡器       37         3.2 复位时间       37         3.3 时钟结构       38         3.3.1 系统时钟结构       38         3.3.2 振荡器控制寄存器 CLKDIV       39         3.3.3 功能时钟控制寄存器 CKCON       36         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.11  | 功能控制寄存器(FUNCCR)      | 36   |

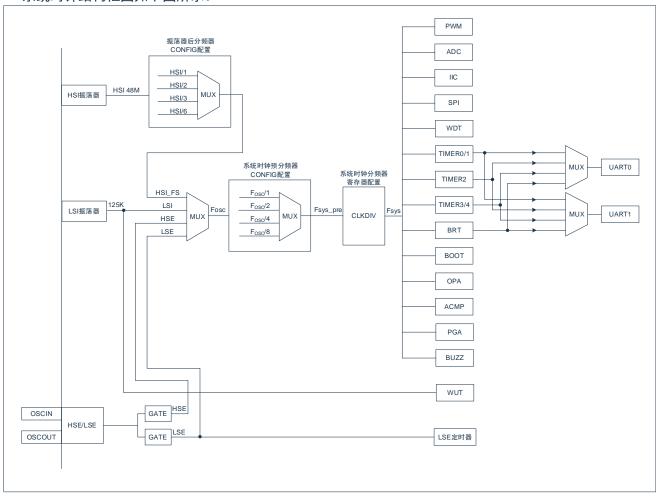

| 3.2 复位时间       37         3.3 时钟结构       38         3.3.1 系统时钟结构       38         3.3.2 振荡器控制寄存器 CLKDIV       39         3.3.3 功能时钟控制寄存器 CKCON       39         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3. | 系统    | 时钟                   | . 37 |

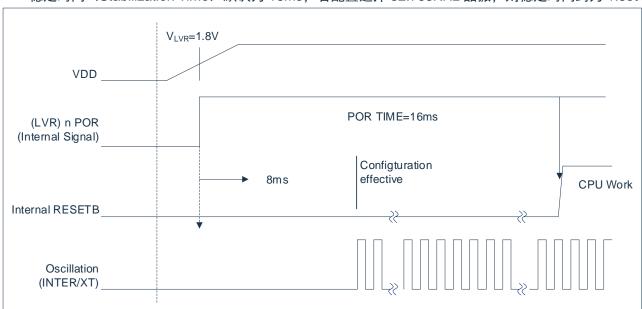

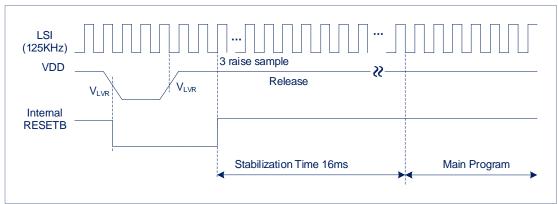

| 3.3       时钟结构       38         3.3.1       系统时钟结构       38         3.3.2       振荡器控制寄存器 CLKDIV       39         3.3.3       功能时钟控制寄存器 CKCON       39         4.       复位       40         4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 3.1   | 系统振荡器                | 37   |

| 3.3.1 系统时钟结构       38         3.3.2 振荡器控制寄存器 CLKDIV       39         3.3.3 功能时钟控制寄存器 CKCON       39         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 3.2   | 复位时间                 | 37   |

| 3.3.2 振荡器控制寄存器 CLKDIV       39         3.3.3 功能时钟控制寄存器 CKCON       39         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.3   | 时钟结构                 | 38   |

| 3.3.3 功能时钟控制寄存器 CKCON       39         4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 3.3.1 | 系统时钟结构               | 38   |

| 4. 复位       40         4.1 上电复位       40         4.2 外部复位       42         4.3 LVR 低压复位       42         4.4 看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 3.3.2 | 振荡器控制寄存器 CLKDIV      | 39   |

| 4.1       上电复位       40         4.2       外部复位       42         4.3       LVR 低压复位       42         4.4       看门狗复位(WDT)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 3.3.3 | 功能时钟控制寄存器    CKCON   | 39   |