# **CMS1237**

# 用户手册

24-bit Sigma-Delta ADC Rev. 2.00

#### 请注意以下有关CMS知识产权政策

\*中微半导体(深圳)股份有限公司(以下简称本公司)已申请了专利,享有绝对的合法权益。与本公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害本公司专利权的公司、组织或个人,本公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨本公司因侵权行为所受的损失、或侵权者所得的不法利益。

\*中微半导体(深圳)股份有限公司的名称和标识都是本公司的注册商标。

\*\*本公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。然而本公司对于规格内容的使用不负责任。文中提到的应用其目的仅仅是用来做说明,本公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。本公司的产品不授权适用于救生、维生器件或系统中作为关键器件。本公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考官方网站 www.mcu.com.cn

### 目录

| 1. | 芯片  | 功   | 能说明                     | 3  |

|----|-----|-----|-------------------------|----|

|    | 1.1 | 功   | 能特性                     | 3  |

|    | 1.2 | 应   | 用场合                     | 3  |

|    | 1.3 | 芯   | 片基本结构功能描述               | ∠  |

|    | 1.4 | 芯   | 片绝对最大极限值                | 4  |

|    | 1.5 | 数   | 字逻辑特性                   | 4  |

|    | 1.6 | C۱  | MS1237 电气特性             | 5  |

|    | 1.7 | 芯   | 片引脚                     | 6  |

| 2. | 芯片  | 功   | 能模块描述                   | 7  |

|    | 2.1 |     |                         |    |

|    | 2.2 |     | 度传感器                    |    |

|    | 2.3 |     |                         |    |

|    | 2.4 | ΑD  | OC 时钟、数据输出速率            | 8  |

|    | 2.5 | 复   | 位和断电模式                  | 9  |

|    | 2.6 |     | 立时间                     |    |

|    | 2.7 | SF  | 의 串口通信                  | 11 |

|    | 2.7 | 7.1 | 数据格式                    | 11 |

|    | 2.7 | 7.2 | 数据准备/数据输入输出(DRDYB/DOUT) | 11 |

|    | 2.7 | 7.3 | 串行时钟输入(SCLK)            | 11 |

|    | 2.7 | 7.4 | 串行数据发送                  | 12 |

|    | 2.7 | 7.5 | 功能配置                    | 13 |

|    | 2.7 | 7.6 | SPI 命令字说明               | 14 |

|    | 2.7 | 7.7 | SPI 通信注意事项              | 14 |

|    | 2.7 | 7.8 | SPI 寄存器                 | 15 |

| 3. | 芯片  | 封   | 装                       | 17 |

|    | 3.1 |     | DP8                     |    |

| 4  |     |     |                         | 18 |

### 1. 芯片功能说明

CMS1237 是一款高精度、低功耗模数转换芯片。支持一路或两路差分输入通道,内置温度传感器和高精度振荡器。CMS1237 的 PGA 可选: 1、2、4、8、16、32、64、128、256。CMS1237 正常模式下的 ADC 数据输出速率可选: 2.5Hz-2.56KHz, 默认为 5Hz。MCU 可以通过 2 线的 SPI 接口 SCLK、DRDYB/DOUT 与 CMS1237 进行通信,对其进行配置,例如通道选择、PGA 选择、输出速率选择等。

#### 1.1 功能特性

- ◆ 内置晶振集成温度传感器

- ◆ 带 Power down 功能

- ◆ 2线 SPI 接口,最快速率为 1.1MHz

- ◆ ADC 功能特性:

- 24 位无失码:

- PGA 放大倍数可选: 1、2、4、8、16、32、64、128、256;

- 1 路 24 位无失码的差分输入,在 PGA=128、输出速率 10Hz 时有效分辨率为 19 位(3.3V);

- PGA=128、ODR=10Hz 时, 等效输入噪声 98nV;

- 输出速率可选: 2.5Hz-2.56KHz。

### 1.2 应用场合

- ◆ 电子秤

- ◆ 液体/气体化学分析

- ◆ 仪表测量

- ◆ 工业过程控制

- ◆ 传感器信号采集

#### 1.3 芯片基本结构功能描述

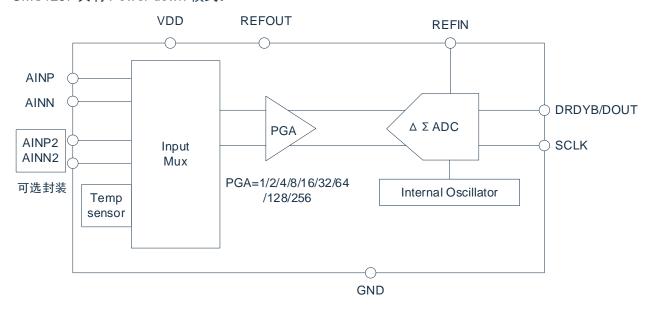

CMS1237 是一款高精度、低功耗 Sigma-Delta 模数转换芯片,内置一路 Sigma-Delta ADC,一路差分输入通道和一路温度传感器,ADC 采用 sigma delta 调制器,通过低噪声仪用放大器结构实现 PGA 放大,放大倍数可选: 1、2、4、8、16、32、64、128、256。在 PGA=128 时,有效分辨率可达 19.2 位(工作在 3.3V)。

CMS1237 内置 RC 振荡器, 无需外置晶振。

CMS1237 可以通过 DRDYB /DOUT 和 SCLK 进行多种功能模式的配置,例如用作温度检测、PGA 增益选择、ADC 数据输出速率选择等等。

CMS1237 具有 Power down 模式。

图 1-1: CMS1237 原理框图

### 1.4 芯片绝对最大极限值

表 1-1: CMS1237 极限值

| 名称       | 符号  | 最小值  | 最大值      | 单位 |

|----------|-----|------|----------|----|

| 电源电压     | VDD | -0.3 | 4.4      | V  |

| 数字管脚输入电压 | -   | -0.3 | DVDD+0.3 | V  |

| 工作温度     | -   | -40  | 85       | °C |

### 1.5 数字逻辑特性

表 1-2: CMS1237 数字逻辑特性

| 秋 1 2 1 0 M 0 1 2 0 7 |          |     |          |      |    |

|-----------------------|----------|-----|----------|------|----|

| 参数                    | 最小值      | 典型值 | 最大值      | 单位   | 条件 |

| VIH                   | 0.7xDVDD | -   | DVDD+0.1 | V    | -  |

| VIL                   | DGND     | -   | 0.3xDVDD | bits | -  |

| VOH                   | DVDD-0.4 | -   | DVDD     | bits | -  |

| VOL                   | DGND     | -   | 0.2xDVDD | bits | -  |

| 串口时钟 SCLK 工作频率        | -        | -   | 1.1      | MHz  | -  |

### 1.6 CMS1237 电气特性

表 1-3-a: CMS1237 电气特性

| 参数       | 最小值       | 典型值         | 最大值      | 单位       | 条件          |

|----------|-----------|-------------|----------|----------|-------------|

| 模拟输入     |           |             |          | <u>.</u> |             |

| 满幅差分输入电压 | -VREF/PGA | -           | VREF/PGA | V        | -           |

| 共模输入电压   | AGND+0.75 | -           | AVDD-1   | V        | -           |

| 差分输入阻抗   | -         | -           | 40       | Mohm     | -           |

| 系统性能     |           |             |          |          |             |

| 分辨率      | -         | 24          | -        | bits     | -           |

| 输出速率     | 2.5       | 5           | 2.56K    | Hz       | -           |

| 建立时间     | -         | -           | 3        | 转换周期     | 全建立         |

| 有效分辨率    | -         | 19.2 (3.3V) | -        | bits     | PGA=128,5Hz |

| 失调误差     | -         | ±2          | -        | uV       | PGA=128,5Hz |

| 增益误差     | -         | ±1          | -        | %        | -           |

| 参考电压输入   | 0.5       | VDD         | 1.1VDD   | V        | -           |

| 参考电压输出   | -         | VDD         | -        | -        | -           |

| 时钟       | -         | 328KHz      | -        | -        | -           |

| 温感       | -         | -           | ±4       | °C       | -           |

| 电源电气特性   |           |             |          |          |             |

| 电源电压     | 2.5       | 3.3         | 4.4      | V        | -           |

| 正常工作电流   | -         | 1.7         | -        | mA       | -           |

| 休眠模式电流   | -         | 0.05        | -        | uA       | -           |

表 1-3-b 是 CMS1237 在不同的输出速率、不同的 PGA 增益条件下的有效分辨率(Effective Resolution)。 测试条件: 电源电压 3.3V, 温度 27 度,参考电压 3.3V, 输入共模电压 1.65V, 输入差分短接。

Effective Resolution=Log2 (Full\_Scale\_Range / RMS\_Noise)

表 1-3-b: CMS1237 的有效分辨率

| 77                      |             |        |       |       |      |        |      |       |       |

|-------------------------|-------------|--------|-------|-------|------|--------|------|-------|-------|

|                         | FADC        |        |       |       | 328  | K (0b) |      |       |       |

| Effective<br>Resolution | OSR         | 64     | 128   | 256   | 1024 | 4096   | 8192 | 16384 | 32768 |

| rtocordion              | ODR (Hz)    | 1281.3 | 640.6 | 320.3 | 80.1 | 20.0   | 10.0 | 5.0   | 2.5   |

|                         | 2 (0000b)   | 15.1   | 16.7  | 17.7  | 18.1 | 19.0   | 20.0 | 20.3  | 20.5  |

|                         | 4 (0001b)   | 14.8   | 16.4  | 17.5  | 18.1 | 19.0   | 19.2 | 19.5  | 19.6  |

|                         | 8 (0011b)   | 14.4   | 16.1  | 17.3  | 18.2 | 18.0   | 18.3 | 18.3  | 18.5  |

| PGA Gain                | 16 (0100b)  | 14.8   | 16.5  | 17.5  | 18.2 | 19.1   | 19.2 | 19.4  | 19.6  |

| PGA Gaili               | 32 (0101b)  | 14.2   | 16.1  | 17.2  | 18.0 | 18.4   | 18.4 | 18.5  | 18.6  |

|                         | 64 (0110b)  | 14.9   | 16.4  | 17.5  | 18.2 | 19.8   | 19.9 | 20.2  | 20.2  |

|                         | 128 (0111b) | 14.3   | 16.0  | 17.1  | 18.4 | 18.9   | 19.0 | 19.2  | 19.4  |

|                         | 256 (1000b) | 14.1   | 15.6  | 16.6  | 17.7 | 17.9   | 18.1 | 18.2  | 18.2  |

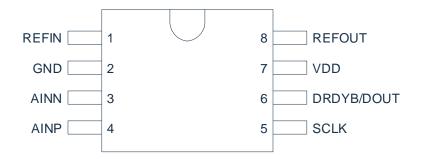

### 1.7 芯片引脚

表 1-4: 引脚说明

| 引脚号 | 引脚名称       | 输入/输出 | 说明            |

|-----|------------|-------|---------------|

| 1   | REFIN      | Al    | 基准输入          |

| 2   | GND        | Р     | DVDD+0.3      |

| 3   | AINN       | Al    | 通道负输入         |

| 4   | AINP       | Al    | 通道正输入         |

| 5   | SCLK       | DI    | SPI 时钟输入接口    |

| 6   | DRDYB/DOUT | DI/DO | SPI 数据输入\输出接口 |

| 7   | VDD        | Р     | 电源            |

| 8   | REFOUT     | Р     | 可控电源输出        |

### 2. 芯片功能模块描述

#### 2.1 模拟输入前端

CMS1237 中有 1 路 ADC,集成了 1 路差分输入,信号输入可以是差分输入信号 AINP、AINN,(或者 10 脚的 AINP2、AINN2),也可以是温度传感器的输出信号,输入信号的切换由寄存器(CH\_SEL[2:0])控制。 000=通道 1;001=通道 1 交换输入(系统斩波);010=温度;011=内短;100=通道 1 直接输入 ADC;101=通道 1 直接输入 ADC;110=BG;111=内短直接输入 ADC。

### 2.2 温度传感器

芯片内部提供温度测量功能。建议采用 PGA 增益 8, ADC 速度为 640Hz 的配置。温度传感器需要进行单点校正。校正方法:在某个温度点 A 下,使用温度传感器进行测量得到码值 Ya。那么其他温度点 B 对应的温度= Yb\*(273.15+A)/Ya-273.15。A 温度单位是摄氏度。Ya 是 A 点对应温度码值。Yb 是 B 点对应温度码值。

对于参考电压可能变化的应用场合(如 Ratio Metric 测量,参考电压的绝对值不重要),可选择通过测量 BG 间接测量出实时的参考电压,进而计算出实时的温度。

#### 2.3 低噪声 PGA 放大器

CMS1237 提供了一个基于斩波技术的低噪声、低漂移的 PGA 放大器与桥式传感器差分输出连接,通过 PGA\_SEL[3:0] 来配置 2 、4、8、16、32、64 、128、256 等不同的 PGA 。当使用 PGA=2, 4, 8 时,第一级低噪声 PGA 放大器会被关断以节省功耗。当使用低噪声 PGA 放大器时,输入范围在 GND+0.75V 到 VDD-1V 之间,超出这个范围,会导致实际性能下降。当模拟输入跳过 PGA,直接输入至 ADC 时,增益为 1。

### 2.4 ADC 时钟、数据输出速率

CMS1237 使用内部时钟来提供系统所需要的时钟频率,可通过 FADC 选择 328KHz 或者 656KHz。ADC 的输出速率可以通过 FADC、OSR[2:0]进行配置。

表 2-1: 时钟、输出速率

| FADC | OSR[2:0] | 输出速率    | ADC 时钟 |

|------|----------|---------|--------|

| 0    | 000      | 2.5Hz   | 328KHz |

| 0    | 001      | 5Hz     | 328KHz |

| 0    | 010      | 10Hz    | 328KHz |

| 0    | 011      | 20Hz    | 328KHz |

| 0    | 100      | 80Hz    | 328KHz |

| 0    | 101      | 320Hz   | 328KHz |

| 0    | 110      | 640Hz   | 328KHz |

| 0    | 111      | 1.28KHz | 328KHz |

| 1    | 000      | 5Hz     | 656KHz |

| 1    | 001      | 10Hz    | 656KHz |

| 1    | 010      | 20Hz    | 656KHz |

| 1    | 011      | 40Hz    | 656KHz |

| 1    | 100      | 160Hz   | 656KHz |

| 1    | 101      | 640Hz   | 656KHz |

| 1    | 110      | 1.28KHz | 656KHz |

| 1    | 111      | 2.56KHz | 656KHz |

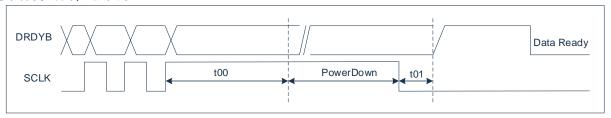

### 2.5 复位和断电模式

当芯片上电时,内置上电复位电路会产生复位信号,使芯片自动复位。当 SCLK 从低电平变高电平并保持在高电平超过 100µs,CMS1237 即进入 PowerDown 模式,此时功耗低于 0.05uA。当 SCLK 重新回到低电平时,芯片会重新进入正常工作状态。当系统由 PowerDown 重新进入正常工作模式时,此时所有功能配置为 PowerDown 之前的状态,不需要进行功能配置。

断电模式示意图如下图所示。其中 t00 表示 SCLK 高电平保持时间,最小为 100us; t01 表示 SCLK 下降 后低电平保持时间,最小为 10us。

图 2-1: 断电模式示意图

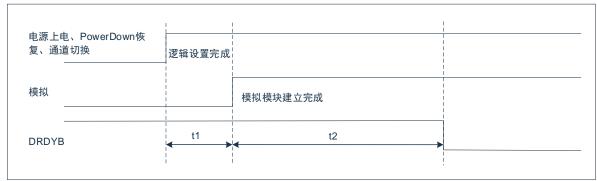

### 2.6 建立时间

CMS1237 的建立时间为均为 3 个转换周期,与所选择的输出速率无关。

图 2-2: 数据建立过程 1

图 2-3:数据建立过程 2

表 2-2: 建立时间

| 参数   | 描述                              | 最小值 | 典型值 | 最大值 | 单位   |

|------|---------------------------------|-----|-----|-----|------|

| 建立时间 |                                 |     |     |     |      |

| t1   | 上电、PowerDown 恢复时间\通道切换后恢<br>复时间 | -   | 0.4 | -   | ms   |

| t2   | 数据建立时间                          |     | 3   | -   | 转换周期 |

| t3   | PGA、通道、速率切换后恢复时间                | -   | 0.8 | -   | us   |

#### 2.7 SPI 串口通信

CMS1237 中采用 2 线 SPI 串行通信,通过 SCLK 和 DRDYB/DOUT 可以实现数据的接收以及功能配置。

#### 2.7.1 数据格式

CMS1237 输出的数据为数字输出码为 24 位的 2 进制补码,其中 B23 为符号位,0 为正,1 为负。最高位 (MSB) 最先输出。下表为不同模拟输入信号对应的理想输出码。

模拟输入由压 十进制码 数据 十六进制 B12 B11 B22 B21 B20 B19 B18 B17 B15 B14 B13 B10 В9 B8 B7 B5 B4 ВЗ B1 B0 B1 B[23:0] Vref-1LSB 0 1 1 1 1 1 1 8388607 7FFFFF 2LSB 1 000002 1LSB 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 000001 0 0 0 0 0 0 0 0 0 0 0 000000 FFFFF -1LSB -2I SB FEFFE -Vref 0 0 0 0 0 0 0 0 0 0 0 -8388608 800000

表 2-3: 数据格式

#### 2.7.2 数据准备/数据输入输出(DRDYB/DOUT)

DRDYB/DOUT 引脚有 4 个用途。第一,当输出为低时,表示新的数据已经转换完成;第二,作为数据输出引脚,当数据准备好后,在第 1 个 SCLK 的上升沿后,DRDYB/DOUT 输出转换数据的溢出位。在每一个 SCLK 的上升沿,数据会自动移 1 位。在 24 个 SCLK 后将所有的 24 位数据读出,如果这时暂停 SCLK 的发送,DRDYB/DOUT 会保持最后一位的数据,直到下一个数据准备好之前拉高,此后当 DRDYB/DOUT 被再次拉低,表示新的数据已经转换完成,可进行下一个数据读取;第三,在第 25、26 个 SCLK 时,输出寄存器状态更新标志;第四,作为寄存器数据写入或读出引脚,当需要配置寄存器或读取寄存器值时,SPI 需要发送 46 个 SCLK,根据 DRDYB/DOUT 输入的命令字,判断是写寄存器操作还是读寄存器操作。

#### 2.7.3 串行时钟输入(SCLK)

串行时钟输入 SCLK 是一个数字引脚。这个信号应保证是一个干净的信号,毛刺或慢速的上升沿都会可能导致读取错误数据或误入错误状态。因此,应保证 SCLK 的上升和下降时间都小于 50ns。

#### 2.7.4 串行数据发送

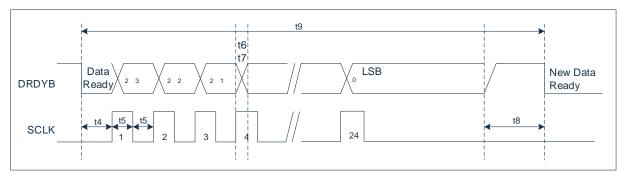

图 2-4: 读取数据时序图 1

图 2-5: 读取数据时序图 2

CMS1237 可以持续的转换模拟输入信号,当将 DRDYB/DOUT 拉低后,表明数据已经准备好接受,输入的第一个 SCLK 来就可以将输出的最高位读出,在 24 个 SCLK 后将所有的 24 位数据读出,如果这时暂停 SCLK 的发送,DRDYB/DOUT 会保持最后一位的数据,直到其被拉高,如图 2-4 所示时序图 1。

如果是持续发送 SCLK,则第 25 和 26 个 SCLK 输出配置寄存器是否有写操作标志,第 25 个 SCLK 对应的 DRDYB/DOUT 为 1 时表明配置寄存器 Config 被写入了新的值,第 26 个 SCLK 对应的 DRDYB/DOUT 为 芯片扩展保留位,目前输出一直为 0,通过第 27 个 SCLK 可以将 DRDYB/DOUT 拉高,此后当 DRDYB/DOUT 被再次拉低,表示新的数据已经准备好接受,进行下一个数据的转换。其基本时序如图 2-5 时序图 2 所示。

| 参数 | 描述                          | 最小值 | 典型值    | 最大值 | 单位 |

|----|-----------------------------|-----|--------|-----|----|

| t4 | DRDYB/DOUT 变低后到第一个 SCLK 上升沿 | -   | 2      | 1   | ns |

| t5 | SCLK 高电平或低电平脉宽              | 455 | -      | -   | ns |

| t6 | SCLK 上升沿到新数据有效(传输延迟)        | 455 | -      | -   | ns |

| t7 | SCLK 上升沿到旧数据位有效(保持时间)       | -   | 1      | 455 | ns |

| t8 | 数据更新,不允许读之前的数据              | -   | 26     | 1   | us |

|    | 转换时间,10Hz                   | -   | 100    | -   | ms |

| t9 | 转换时间,40Hz                   | -   | 25     | 1   | ms |

|    | 转换时间,640Hz                  | -   | 1.5625 | -   | ms |

表 2-4: 读取数据时间表

#### 2.7.5 功能配置

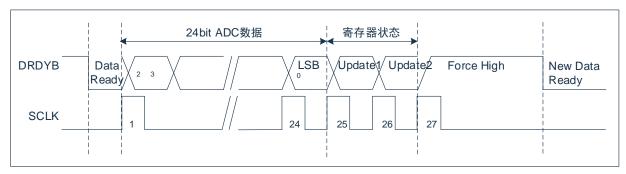

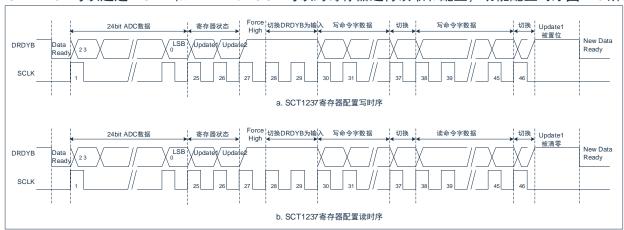

CMS1237 可以通过 SCLK 和 DRDYB/DOUT 可以对寄存器进行读取和配置,功能配置时序图 2-6 所示:

图 2-6: 功能配置时序图 3

功能配置过程简述,判断到 DRDYB/DOUT 由高变低之后:

- 1) 第 1 个到第 24 个 SCLK,读取 ADC 数据。如果不需要配置寄存器或者读取寄存器,可以省略下面的步骤。

- 2) 第 25 个到第 26 个 SCLK, 读取寄存器写操作状态。

- 3) 第 27 个 SCLK, 芯片把 DRDYB/DOUT 输出拉高。

- 4) 第 28 个到第 29 个 SCLK, 切换 DRDYB/DOUT 为输入。

- 5) 第 30 个到第 36 个 SCLK, 输入寄存器写或读命令字数据(高位先输入)。

- 6) 第 37 个 SCLK, 切换 DRDYB/DOUT 的方向(如果是写寄存器, DRDYB/DOUT 为输入;如果是读寄存器, DRDYB/DOUT 为输出)。

- 7) 第 38 个到第 45 个 SCLK, 输入寄存器配置数据或输出寄存器配置数据(高位先输入/输出)。

- 8) 第 46 个 SCLK, 切换 DRDYB/DOUT 为输出,并把 DRDYB/DOUT 拉高。update1/ update2 被置位或清零。

#### 2.7.6 SPI 命令字说明

CMS1237 有 4 个命令字, 命令字的长度为 7bits, 命令字的说明如下:

表 2-5: SPI 命令字说明

| 命令对象(控制字) | 命令字节 | 描述        |

|-----------|------|-----------|

| Config.1  | 0x65 | 写 Config1 |

| Config1   | 0x56 | 读 Config1 |

| Config    | 0x69 | 写 Config2 |

| Config2   | 0x5A | 读 Config2 |

| Config2   | 0x6D | 写 Config3 |

| Config3   | 0x5E | 读 Config3 |

| Config.4  | 0x61 | 写 Config4 |

| Config4   | 0x52 | 读 Config4 |

#### 2.7.7 SPI 通信注意事项

如前所述, CMS1237 可以有三类通信时序, 分别为:

时序 1: 读取 24 位 ADC 转换数据

时序 2: 读取 24 位 ADC 转换数据+寄存器状态

时序 3: 读取 24 位 ADC 转换数据+寄存器状态+读写控制字

#### 发送三类时序时需注意:

- 1) 读取的数据是发送时序前最后一次 ADC 转换完成的结果;

- 2) 上电后建议 80ms 以后再给时序, 在此之前任何 SCLK 信号将被屏蔽;

- 3) 需判断 DRDYB 产生了下降沿后,再发送时序;

- 4) 发送任何时序时间从 DRDYB 下降沿到数据全部发送完成的时间小于一个转换时间(即在两次下降沿 之间完成时序发送)。

如果不满足上述条件,发送时序的完整时间则有可能超过一个转换周期。

#### 2.7.8 SPI 寄存器

CMS1237 有四组控制寄存器。其默认值如下。

表 2-6: SPI 命令字默认值

| 序号 | 名称          | 默认值(bin)   | 说明              |

|----|-------------|------------|-----------------|

| 1  | adcon1[7:0] | "00000110" | Config1(常用控制字)  |

| 2  | adcon2[7:0] | "00010000" | Config2(扩展的控制字) |

| 3  | adcon3[7:0] | "10001000" | Config3(扩展的控制字) |

| 4  | adcon4[7:0] | "10000000" | Config4(扩展的控制字) |

#### 表 2-7: 控制字定义(1)

| Register ADO | Register ADCON1 |         |                                                                              |  |  |  |

|--------------|-----------------|---------|------------------------------------------------------------------------------|--|--|--|

| Bit Number   | Bit Mnemonic    | DEFAULT | Description                                                                  |  |  |  |

| 7            | Test            | 0       | 1 为中测位,REFOUT 引脚输出 clk_adc                                                   |  |  |  |

| 6            | REFO_OFF        | 0       | REFO 输出,默认打开                                                                 |  |  |  |

| 5            |                 |         | OSR 设置                                                                       |  |  |  |

| 4            | OSR[2:1]        | 11      | 111=32768, 110=16384, 101=8192, 100=4096, 011=1024, 010=256, 001=128, 000=64 |  |  |  |

| 3            |                 |         |                                                                              |  |  |  |

| 2            | DCA SELIZIO     | 0110    | PGA增益:                                                                       |  |  |  |

| 1            | PGA_SEL[3:0]    |         | 0000=2, 0001=4, 0010=8, 0011=8, 0100=16, 0101=32, 0110=64,                   |  |  |  |

| 0            |                 |         |                                                                              |  |  |  |

#### 表 2-8: 控制字定义(2)

| Register ADCON2 |              |         |                                                            |  |

|-----------------|--------------|---------|------------------------------------------------------------|--|

| Bit Number      | Bit Mnemonic | DEFAULT | Description                                                |  |

| 7               |              |         | 通道选择                                                       |  |

| 6               | CH SEL[2:0]  | 000     | 000=通道 1, 001=通道一交换(系统斩波), 010=温度, 011=                    |  |

| 5               |              |         | 内短; 100=通道 1 直接 ADC; 101=通道 1 交换接 ADC; 110=BG; 111=内短接 ADC |  |

| 4               | LPWR         | 1       | 1= lowest power, 0=Highest power                           |  |

| 3               | FADC         | 0       | 0=328KHz,1=656KHz                                          |  |

| 2               | OSR[0]       | 0       | OSR LSB                                                    |  |

| 1               | ENCHOPB      | 0       | 斩波使能,0为打开斩波功能                                              |  |

| 0               | FCHOP_ADC    | 0       | 斩波频率选择,0=16 分频,1=32 分频                                     |  |

#### 表 2-9: 控制字定义(3)

| Register ADCON3 |               |         |                  |

|-----------------|---------------|---------|------------------|

| Bit Number      | Bit Mnemonic  | DEFAULT | Description      |

| 7               |               |         |                  |

| 6               | TRIM_OS[3:0]  | 1000    | PGA 失调控制         |

| 5               |               |         |                  |

| 4               |               |         |                  |

| 3               | DEADZONEI4.01 | 10      | 时钟死区控制,00最小,11最大 |

| 2               | DEADZONE[1:0] |         |                  |

| 1               | 保留            | 0       |                  |

| 0               | PGAENB        | 0       | PGA 使能信号         |

### 表 2-10: 控制字定义(4)

| Register ADCON4 |              |         |                                      |

|-----------------|--------------|---------|--------------------------------------|

| Bit Number      | Bit Mnemonic | DEFAULT | Description                          |

| 7               |              |         |                                      |

| 6               | TDIM DOISO   | 1000    | BG 输出 trim                           |

| 5               | TRIM_BG[3:0] | 1000    | BG 制页 UIII                           |

| 4               |              |         |                                      |

| 3               | 保留           | 0       | -                                    |

| 2               | 保留           | 0       | -                                    |

| 1               | FCHOP[1:0]   | 01      | 00=4 分频, 01=8 分频, 10=16 分频, 11=32 分频 |

# 3. 芯片封装

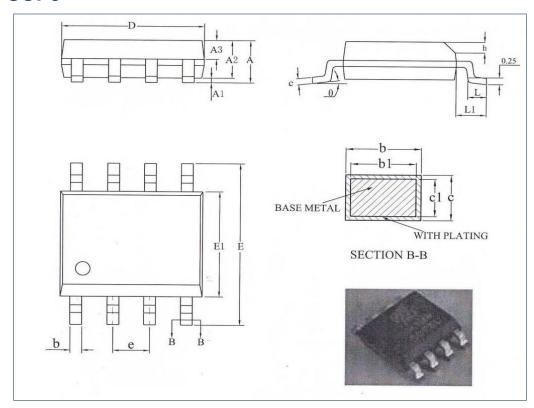

## 3.1 SOP8

| Cumbal | Millimeter |      |       |  |

|--------|------------|------|-------|--|

| Symbol | Min        | Nom  | Max   |  |

| А      | -          | -    | 1.75  |  |

| A1     | 0.10       | -    | 0.225 |  |

| A2     | 1.30       | 1.40 | 1.50  |  |

| А3     | 0.60       | 0.65 | 0.70  |  |

| b      | 0.39       | -    | 0.47  |  |

| b1     | 0.38       | 0.41 | 0.44  |  |

| С      | 0.20       | -    | 0.24  |  |

| c1     | 0.19       | 0.20 | 0.21  |  |

| D      | 4.80       | 4.90 | 5.00  |  |

| E      | 5.80       | 6.00 | 6.20  |  |

| E1     | 3.80       | 3.90 | 4.00  |  |

| е      | 1.27BSC    |      |       |  |

| h      | 0.25       | -    | 0.50  |  |

| L      | 0.5        | -    | 0.80  |  |

| L1     | 1.05REF    |      |       |  |

| θ      | 0          | -    | 8°    |  |

| 版本号   | 时间       | 修改内容                     |  |

|-------|----------|--------------------------|--|

| V1.00 | 2019年6月  | 初始版本                     |  |

| V2.00 | 2020年12月 | 更新寄存器、输出速率、精度、功耗、数据格式等指标 |  |