# CMS32L051 User Manual

Ultra-low-power 32-bit microcontroller based on the ARM® Cortex®-M0+

V1.2.2

Please note the following CMS IP policy

\*Zhongwei Semiconductor (Shenzhen) Co., Ltd. (hereinafter referred to as the Company) has applied for a patent and enjoys absolute legal rights and interests. The patent rights related to the Company's MCUs or other products have not been authorized to be licensed, and any company, organization or individual who infringes the Company's patent rights through improper means will take all possible legal actions to curb the infringer's improper infringement and recover the losses suffered by the Company as a result of the infringement or the illegal benefits obtained by the infringer.

\* The name and logo of Zhongwei Semiconductor (Shenzhen) Co., Ltd. are registered trademarks of the Company.

\* The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not licensed for lifesaving, life-sustaining devices or systems as critical devices. The Company reserves the right to modify the product without prior notice, please refer to the official website www.mcu.com.cn for the latest information.

#### **Documentation Instructions**

This manual is a <u>technical reference manual</u> for CMS32L051 microcontroller products, and <u>the technical</u> <u>reference manual</u> is an application note on how to use this series of products, including the structure, functional description, and function description of each functional module. Details such as operating modes and register configuration.

<u>The Technical Reference Manual</u> is a description of all functional modules in this series of products, please refer to the data sheet for the description of the characteristics of the product (i.e. the function carrying situation).

The data sheet information is as follows:

CMS32L051xx: CMS32L051xx\_datasheet\_vx.x.x. pdf

Usually in the early stage of chip selection, the first thing to see is to look at the <u>data sheet</u> to evaluate whether the product can meet the functional requirements of the design; After basically selecting the required product, it is necessary to check the <u>technical reference manual</u> to determine whether the working mode of each functional module meets the requirements; When determining that the selection enters the programming design phase, a detailed technical <u>reference manual</u> is required to understand the specific implementation of each function and the register configuration. Refer to the <u>data sheet</u> when designing your hardware for information such as voltage, current, drive capability, and pin assignment.

For a detailed description of the Cortex-M0+ core, SysTick timer, and NVIC, please refer to the documentation for the corresponding ARM.

#### Contents

| Docun  | nentation Instructions                                                                                                                                                                                                                      | . 2 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapt  | er 1 CPU                                                                                                                                                                                                                                    | 14  |

| 1.1    | Overview                                                                                                                                                                                                                                    | 14  |

| 1.2    | Cortex-M0+ core features                                                                                                                                                                                                                    | 14  |

| 1.3    | Debugging features                                                                                                                                                                                                                          | 14  |

| 1.4    | SWD interface pin                                                                                                                                                                                                                           | 16  |

| 1.5    | ARM reference document                                                                                                                                                                                                                      | 17  |

| Chapt  | er 2 Pin Function                                                                                                                                                                                                                           | 18  |

| 2.1    | Port function                                                                                                                                                                                                                               | 18  |

| 2.2    | Port multiplexing function                                                                                                                                                                                                                  | 18  |

| 2.3    | Registers for controlling port functions                                                                                                                                                                                                    |     |

| 2.3    | .1 Port mode register (PMxx)                                                                                                                                                                                                                | 21  |

| 2.3    | 5 ( )                                                                                                                                                                                                                                       |     |

| 2.3    | 5 ( )                                                                                                                                                                                                                                       |     |

| 2.3    | 5 ( - )                                                                                                                                                                                                                                     |     |

| 2.3    |                                                                                                                                                                                                                                             |     |

| 2.3    | 5 ( )                                                                                                                                                                                                                                       |     |

| 2.3    |                                                                                                                                                                                                                                             |     |

| 2.3    | · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                           |     |

| 2.3    |                                                                                                                                                                                                                                             |     |

|        | .10 Port input multiplexing function configuration registers (TI10PCFG, TI11PCFG, TI12PCF<br>3PCFG, INTP0PCFG, INTP1PCFG , INTP2PCFG, INTP3PCFG, SDI00PCFG, SCLKI00PCF<br>00PCFG , SDI20PCFG, SCLKI20PCFG, SDAA0PCFG, SCLA0PCFG, RXD1PCFG ) | G,  |

| 2.3    |                                                                                                                                                                                                                                             |     |

| 2.4    | Handling of unused pins                                                                                                                                                                                                                     |     |

| 2.5    | Register setting when using the multiplexed function                                                                                                                                                                                        | 39  |

| 2.5    | .1 Basic idea when using the multiplexed output feature                                                                                                                                                                                     | 39  |

| 2.5    | .2 Example of register settings using port functions and multiplexing functions                                                                                                                                                             | 40  |

| 2.5    | .3 EPWM port configuration method                                                                                                                                                                                                           | 56  |

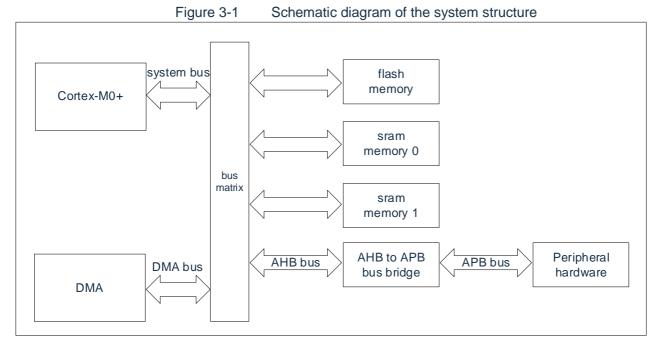

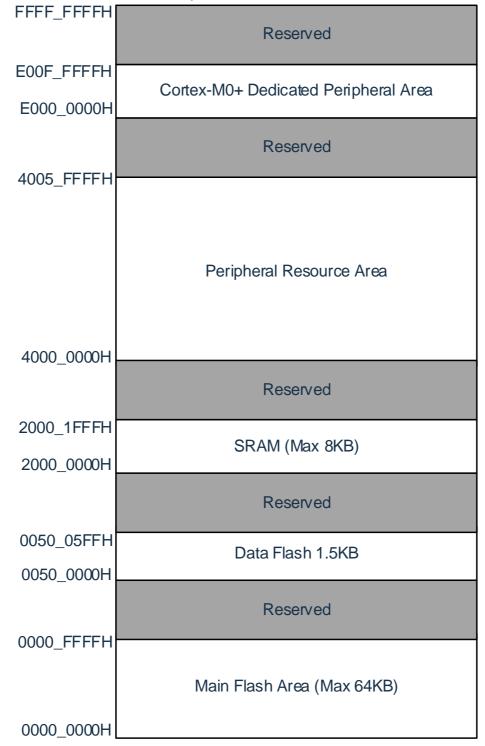

| Chapte | er 3 System Structure                                                                                                                                                                                                                       | 57  |

| 3.1    | Overview                                                                                                                                                                                                                                    | 57  |

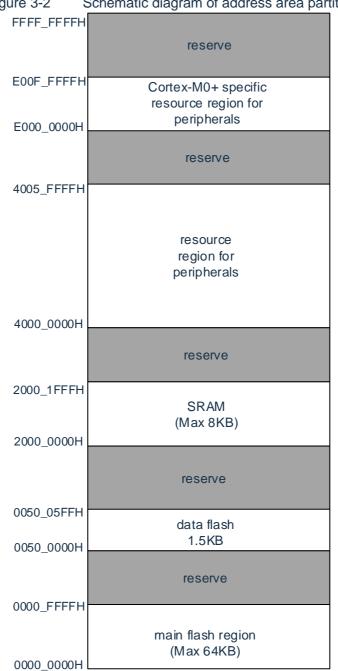

| 3.2    | System address partition                                                                                                                                                                                                                    | 58  |

| Chapt  | er 4 Clock Generation Circuit                                                                                                                                                                                                               | 60  |

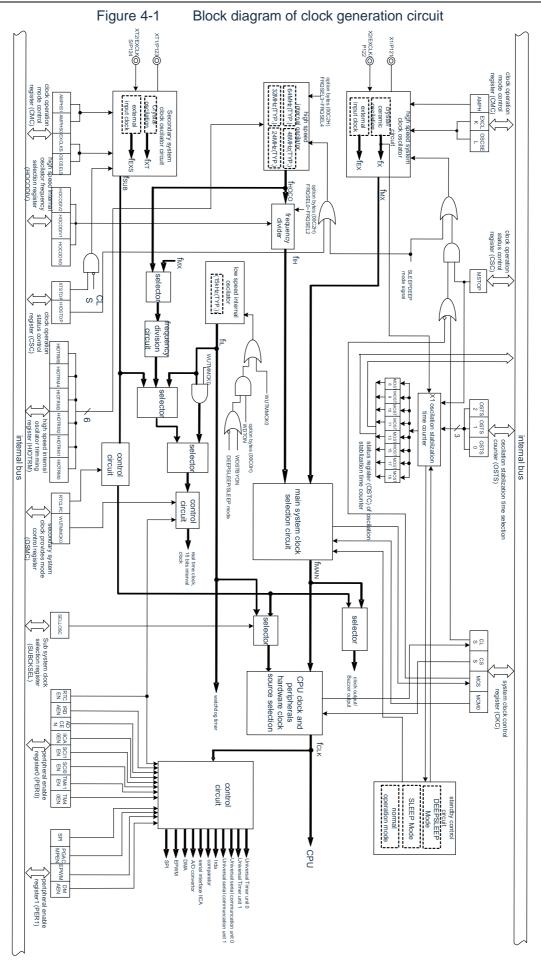

| 4.1    | Function of the clock generation circuit                                                                                                                                                                                                    | 60  |

| 4.2    | Structure of clock generation circuit                                                                                                                                                                                                       | 62  |

| 4.3    | Registers for controlling clock generation circuit                                                                                                                                                                                          | 65  |

| 4.3    | .1 Clock operation mode control register (CMC)                                                                                                                                                                                              | 65  |

| 4.3    | .2 System clock control register (CKC)                                                                                                                                                                                                      | 67  |

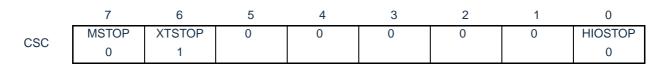

| 4.3    | .3 Clock operation status control register (CSC)                                                                                                                                                                                            | 68  |

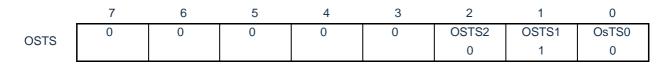

| 4.3    | .4 Status register of the oscillation stabilization time counter (OSTC)                                                                                                                                                                     | 69  |

| 4.3    | 5 ( )                                                                                                                                                                                                                                       |     |

| 4.3    |                                                                                                                                                                                                                                             |     |

| 4.3    | 5 11 5 6 ( )                                                                                                                                                                                                                                |     |

| 4.3    | .8 High-speed internal oscillator frequency selection register (HOCODIV)                                                                                                                                                                    | 77  |

| 4.3.9     | High-speed internal oscillator trim register (HIOTRM)                         | 78  |

|-----------|-------------------------------------------------------------------------------|-----|

| 4.3.10    | Subsystem clock selection register (SUBCKSEL)                                 | 79  |

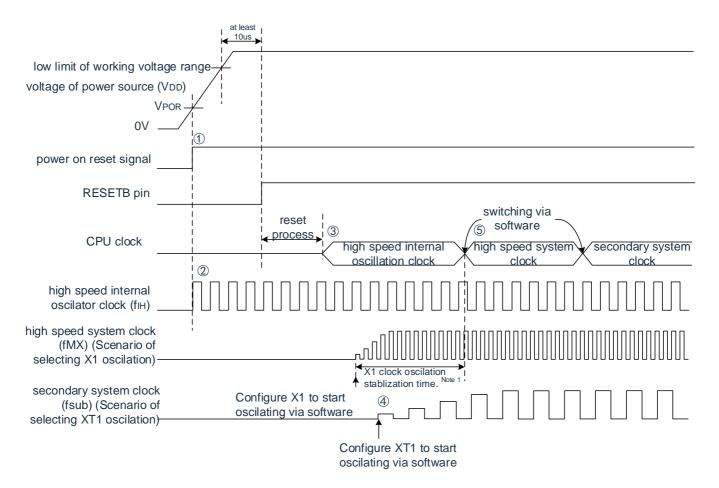

| 4.4 Syst  | em clock oscillation circuit                                                  | 80  |

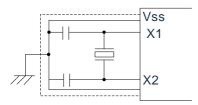

| 4.4.1     | X1 oscillation circuit                                                        | 80  |

| 4.4.2     | XT1 oscillation circuit                                                       | 80  |

| 4.4.3     | High-speed internal oscillator                                                | 84  |

| 4.4.4     | Low-speed internal oscillator                                                 | 84  |

| 4.5 Ope   | ration of clock generation circuit                                            | 85  |

| 4.6 Cloc  | k control                                                                     | 87  |

| 4.6.1     | Example of setting up a high-speed internal oscillator                        | 87  |

| 4.6.2     | Example of setting up an X1 oscillation circuit                               | 89  |

| 4.6.3     | Example of setting up an XT1 oscillation circuit                              | 90  |

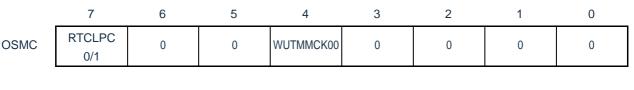

| 4.6.4     | State transition graph of the CPU clock                                       | 91  |

| 4.6.5     | Conditions before CPU clock transfer and processing after transfer            | 97  |

| 4.6.6     | Time required to switch between CPU clock and main system clock               | 99  |

| 4.6.7     | Condition before the clock oscillation stops                                  | 100 |

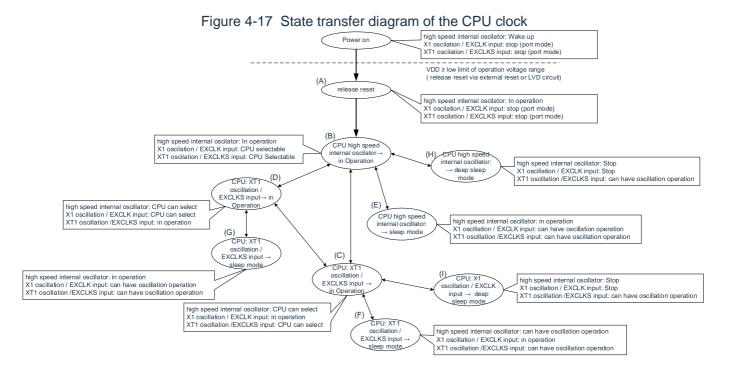

| 4.7 High  | -speed internal oscillation correction                                        | 101 |

| 4.7.1     | High-speed internal oscillation self-adjustment function                      |     |

| 4.7.2     | Register description                                                          | 102 |

| 4.7.3     | Operation description                                                         | 103 |

| 4.7.4     | Precautions for use                                                           | 106 |

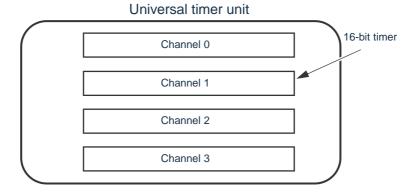

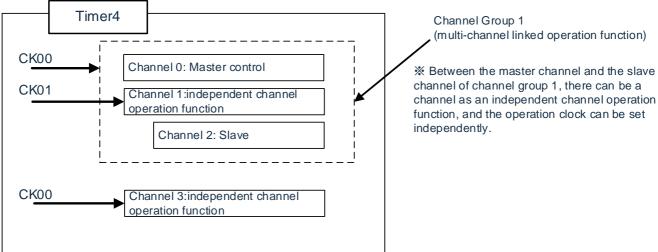

| Chapter 5 | Universal Timer Unit (Timer4)                                                 | 107 |

| 5.1 Fun   | ction of universal timer unit                                                 | 108 |

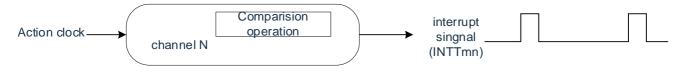

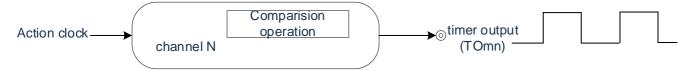

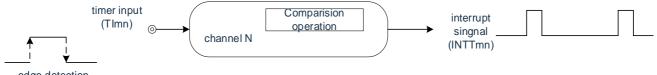

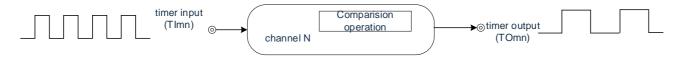

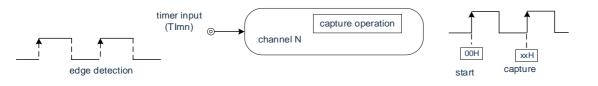

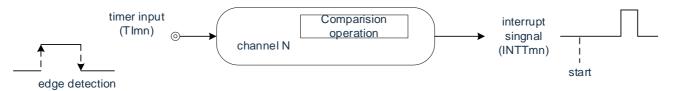

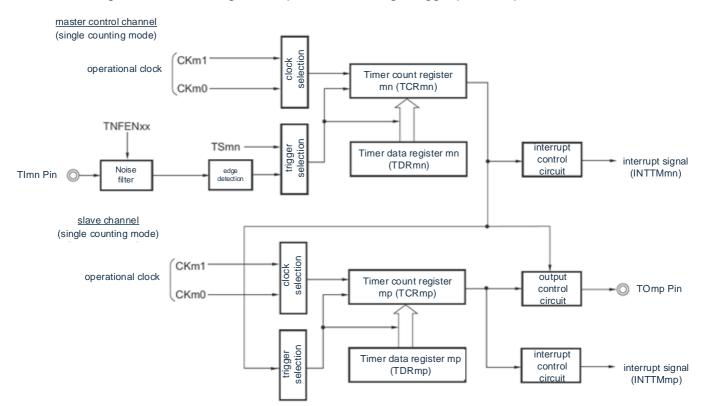

| 5.1.1     | Independent channel operation function                                        | 108 |

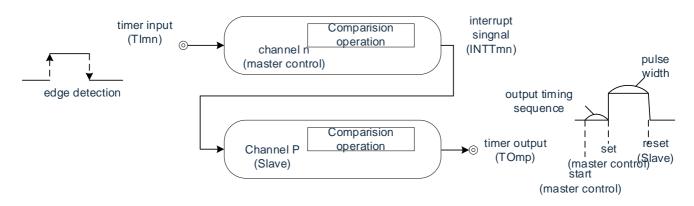

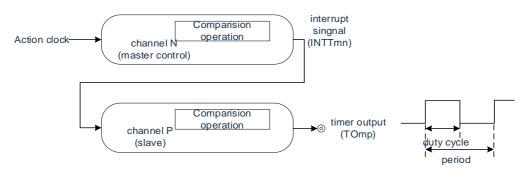

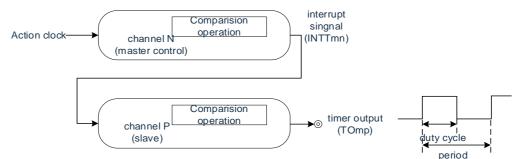

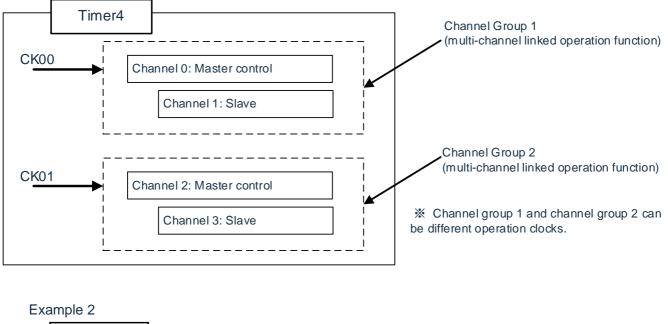

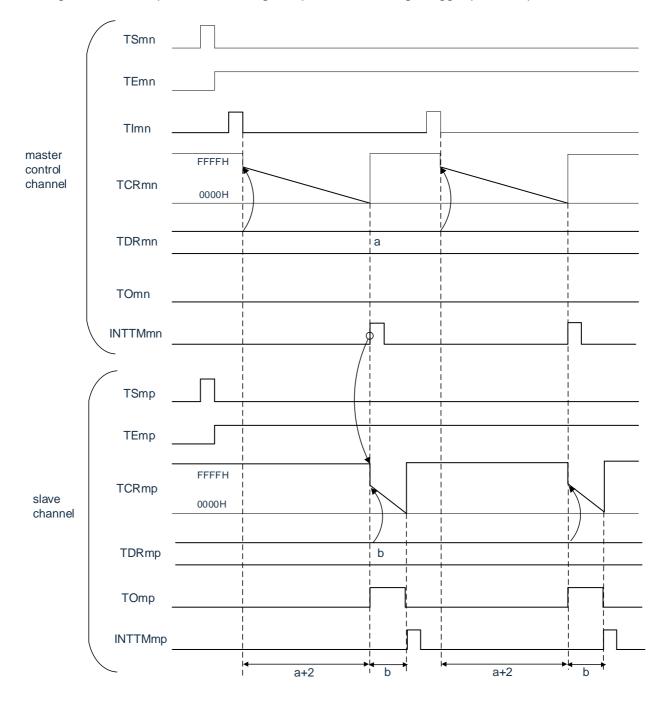

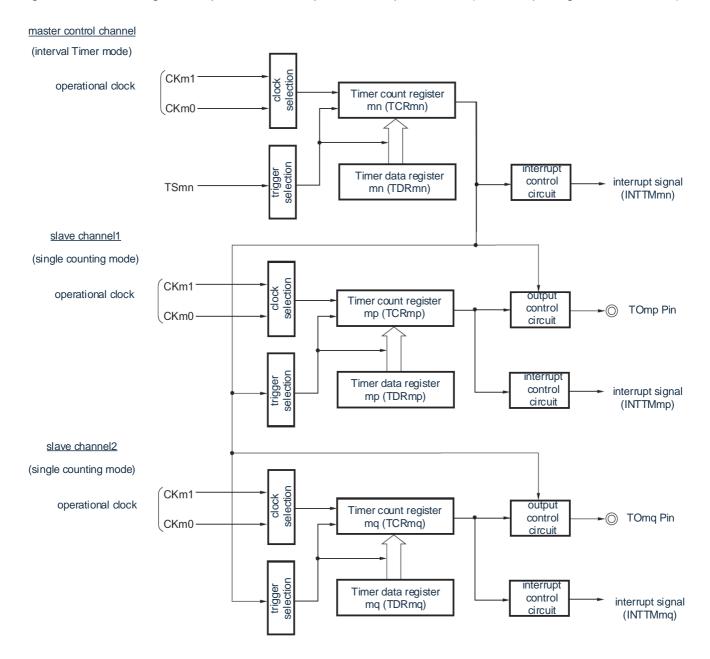

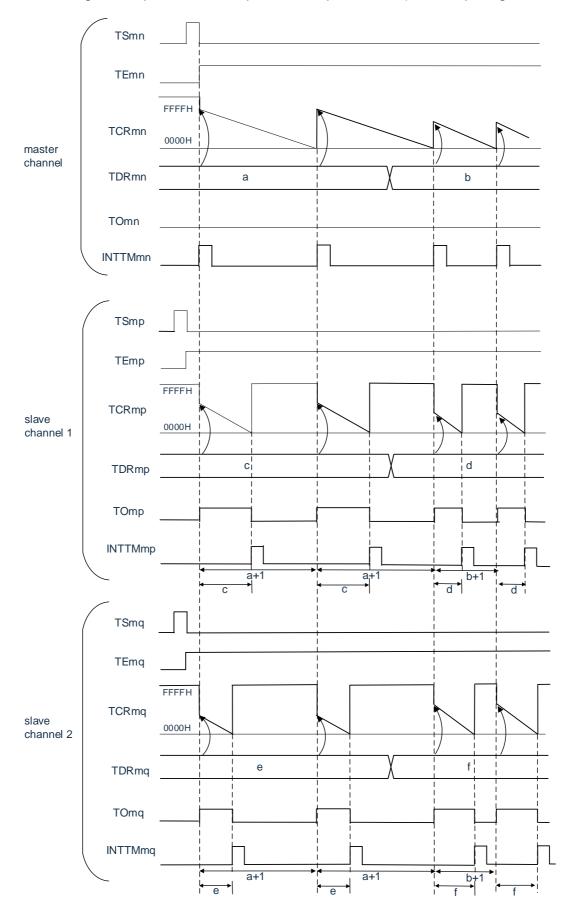

| 5.1.2     | Multi-channel linkage operation function                                      | 110 |

| 5.1.3     | 8-bit timer operation function (limited to Channel 1 and Channel 3 of Unit 0) | 111 |

| 5.1.4     | LIN-bus support functions (channel 3 of unit 0 only)                          | 111 |

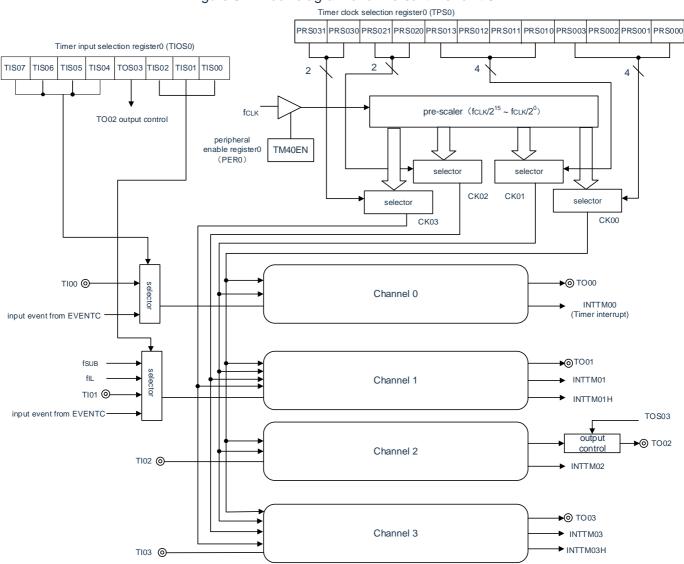

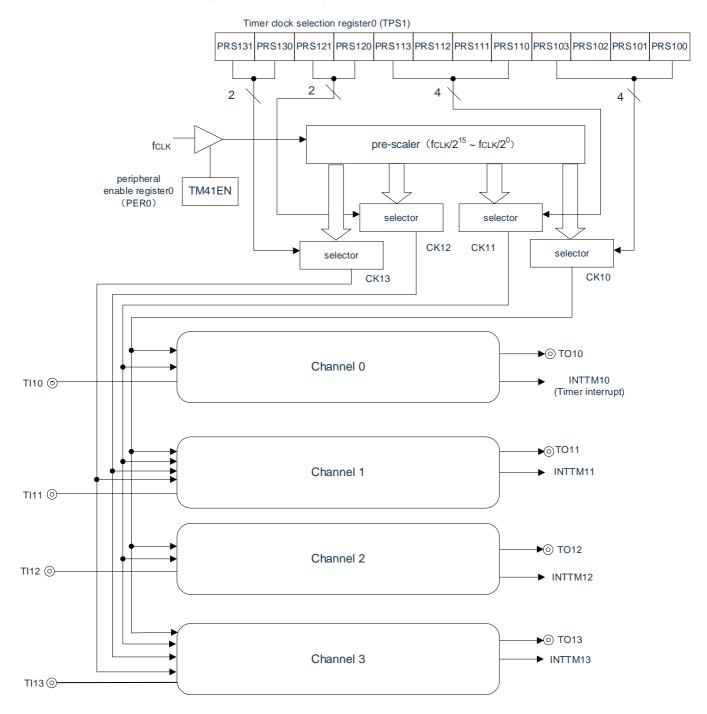

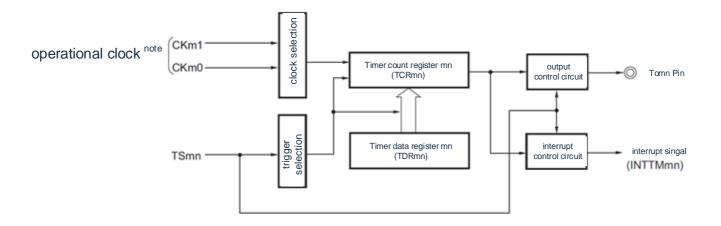

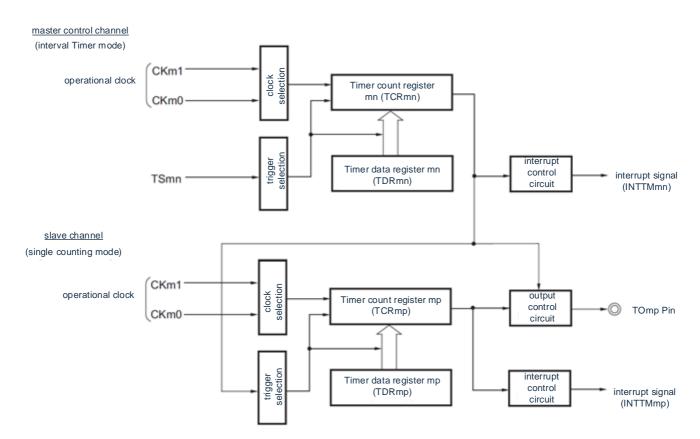

| 5.2 Stru  | cture of the universal timer unit                                             | 112 |

| 5.2.1     | List of universal timer unit 0 registers                                      | 115 |

| 5.2.2     | List of universal timer unit 1 registers                                      | 116 |

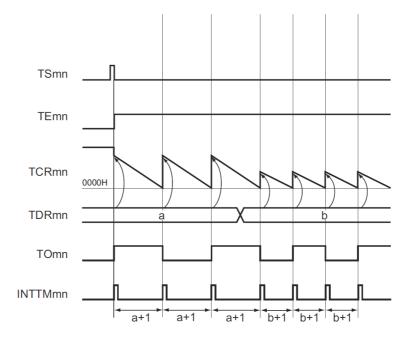

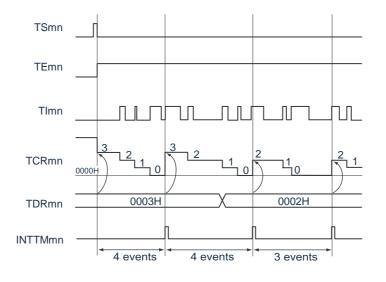

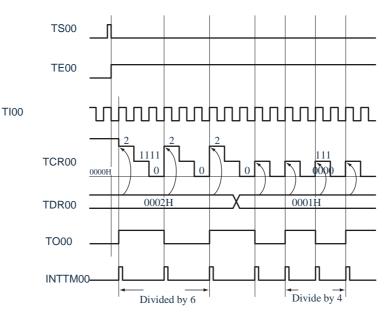

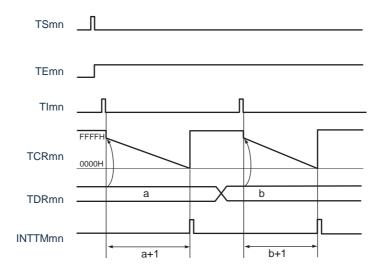

| 5.2.3     | Timer count register mn (TCRmn)                                               | 117 |

| 5.2.4     | Timer data register mn (TDRmn)                                                | 118 |

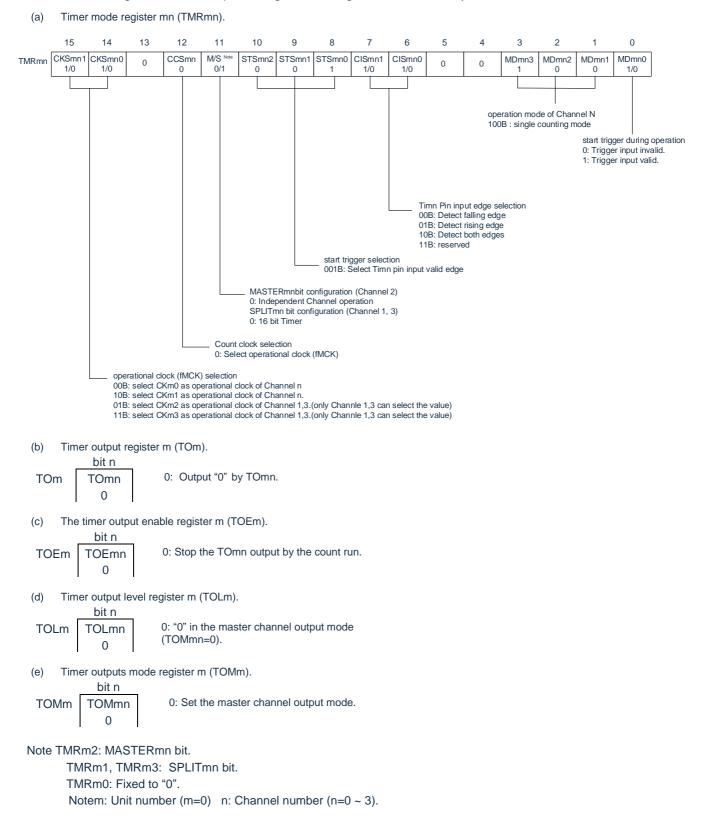

| 5.3 Reg   | isters for controlling general-purpose timer unit                             | 119 |

| 5.3.1     | Peripheral enable register 0 (PER0)                                           | 120 |

| 5.3.2     | Timer clock select register m (TPSm)                                          | 121 |

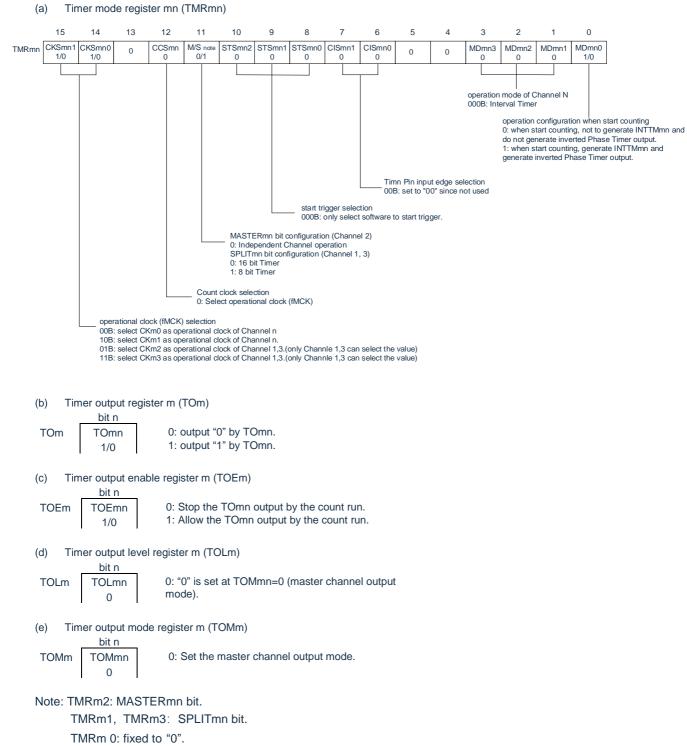

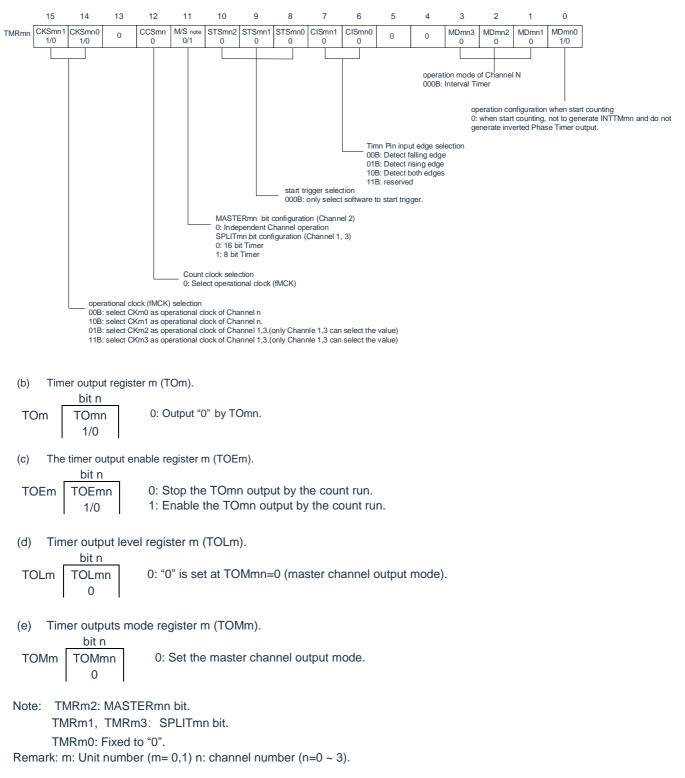

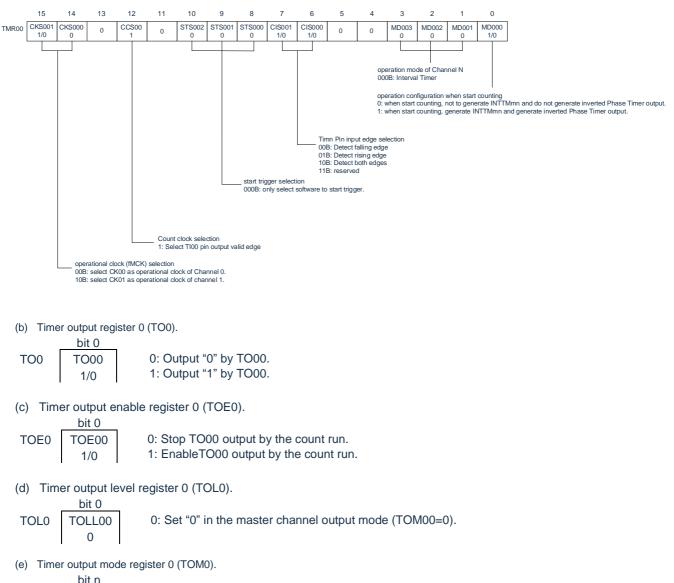

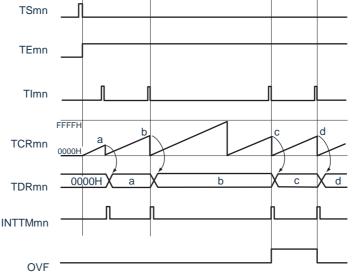

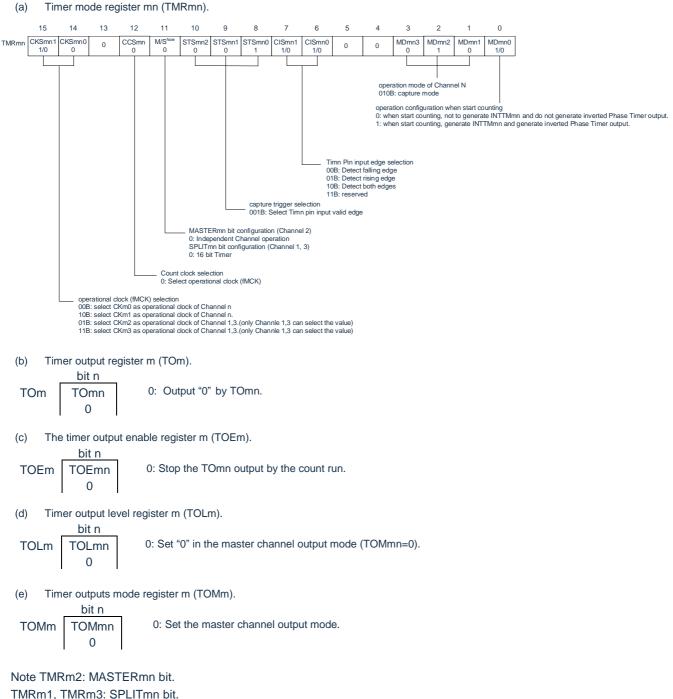

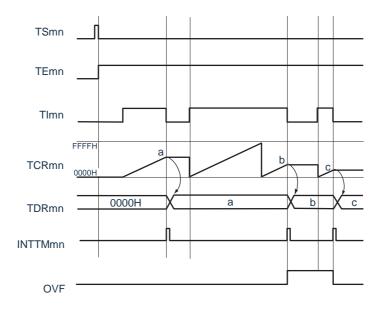

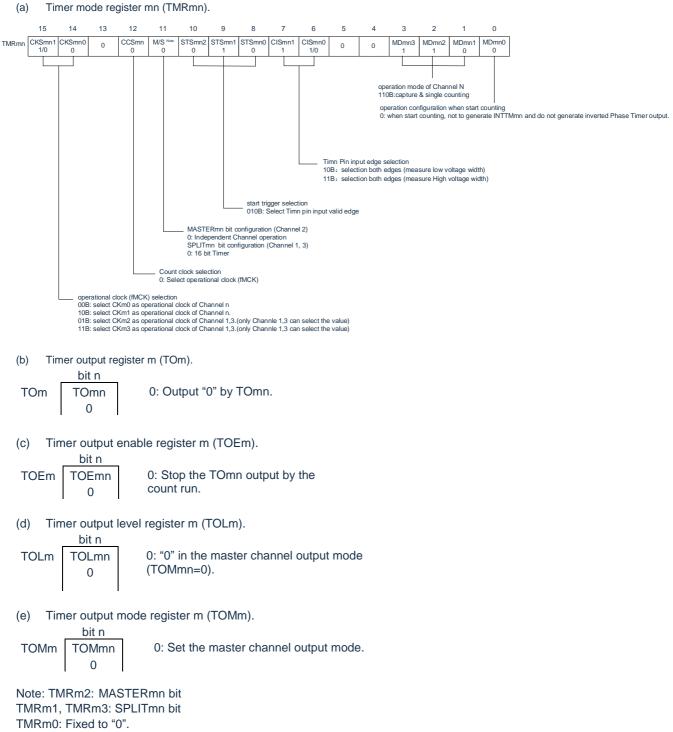

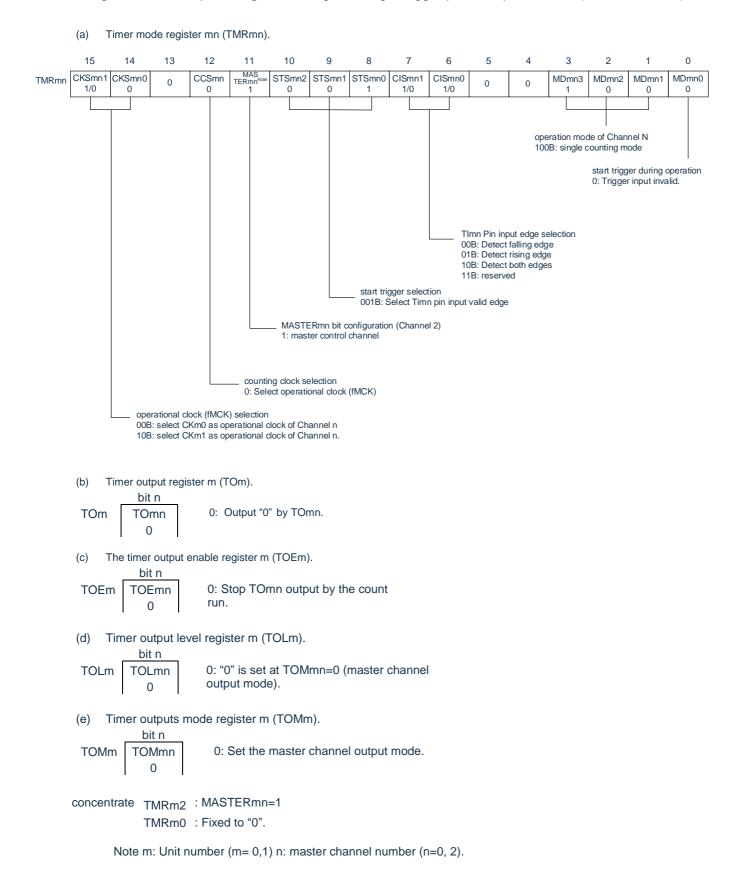

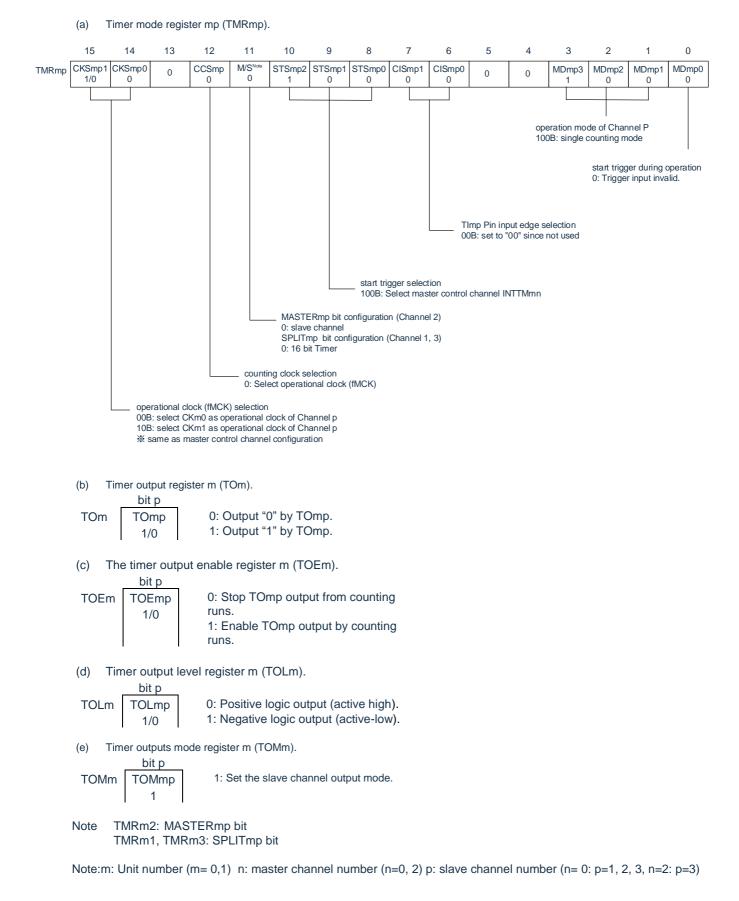

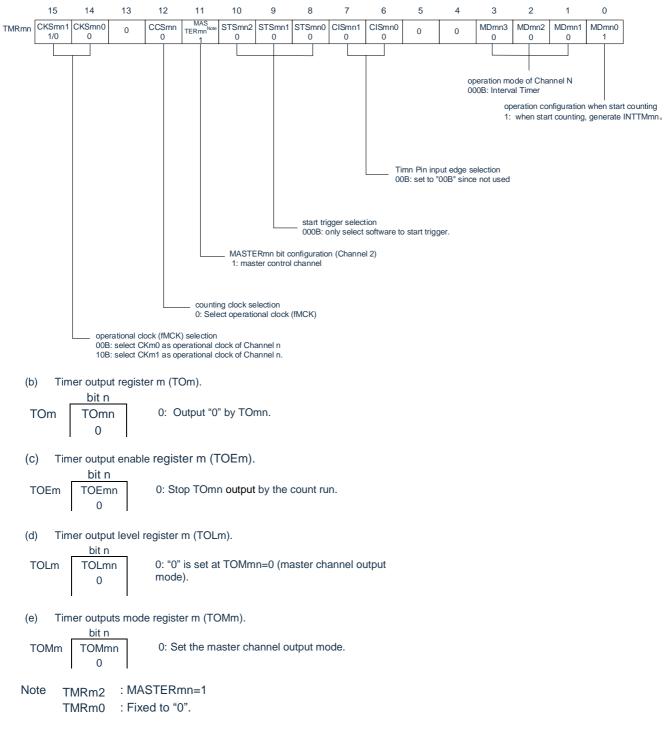

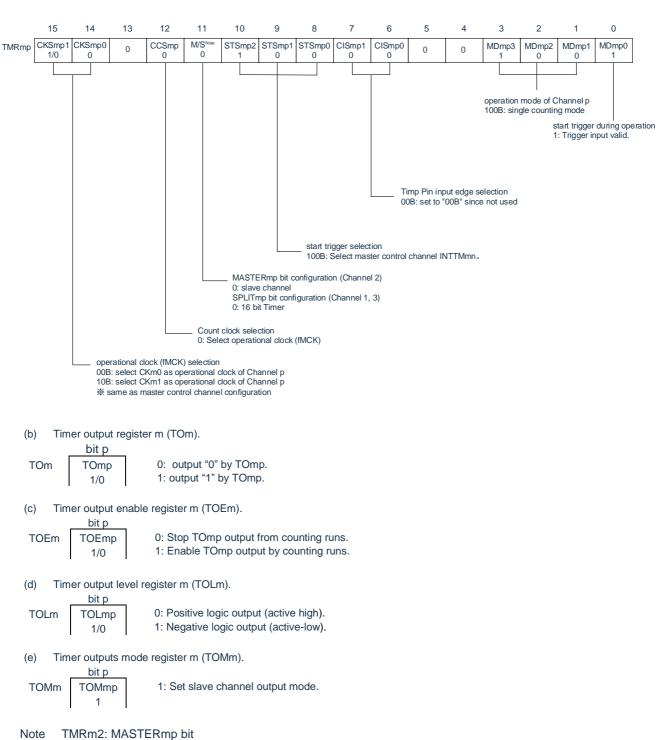

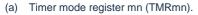

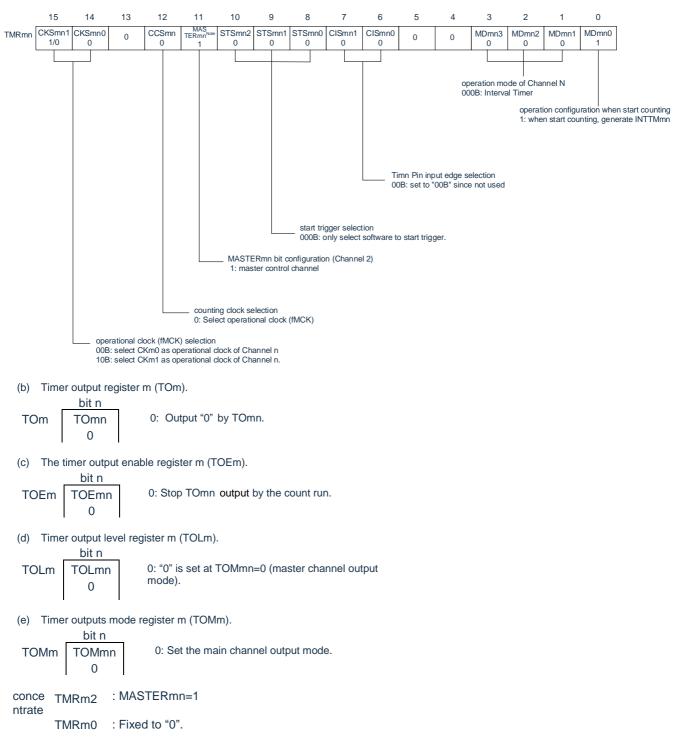

| 5.3.3     | Timer mode register mn (TMRmn)                                                | 124 |

| 5.3.4     | Timer status register mn (TSRmn)                                              | 129 |

| 5.3.5     | Timer channel enable status register m (TEm)                                  | 130 |

| 5.3.6     | Timer channel start register m (TSm)                                          | 131 |

| 5.3.7     | Timer channel stop register m (TTm)                                           | 132 |

| 5.3.8     | Timer input-output select register (TIOS0)                                    | 133 |

| 5.3.9     | Timer output enable register m (TOEm)                                         | 134 |

| 5.3.10    | Timer output register m (TOm).                                                | 135 |

| 5.3.11    | Timer output level register m (TOLm)                                          | 136 |

| 5.3.12    | Timer output mode register m (TOMm)                                           | 137 |

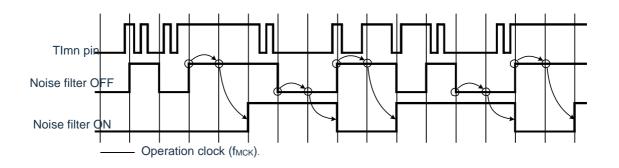

| 5.3.13    | Noise filter enable register 1 (NFEN1)                                        | 138 |

| 5.3.14    | Noise filter enable register 2 (NFEN2)                                        | 139 |

| 5.3.1   | 5 Registers for controlling timer input/output pin port functions                         | 140       |

|---------|-------------------------------------------------------------------------------------------|-----------|

| 5.4 E   | Basic rules of the universal timer unit                                                   | 141       |

| 5.4.1   | Basic rules of the multi-channel linkage operation function                               | 141       |

| 5.4.2   | Basic rules for the 8-bit timer to operate the function (limited to Channel 1 and Channel | 3 of Unit |

| 0).     | 143                                                                                       |           |

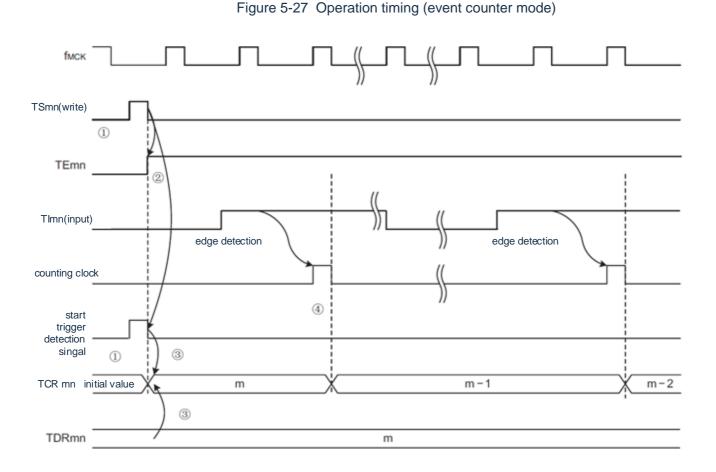

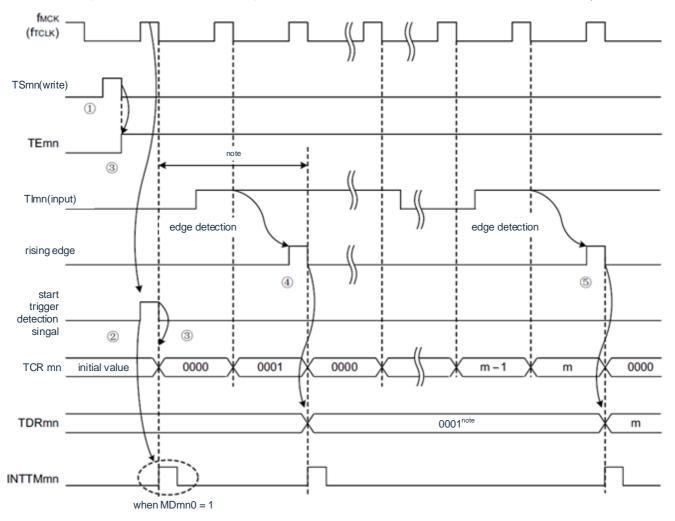

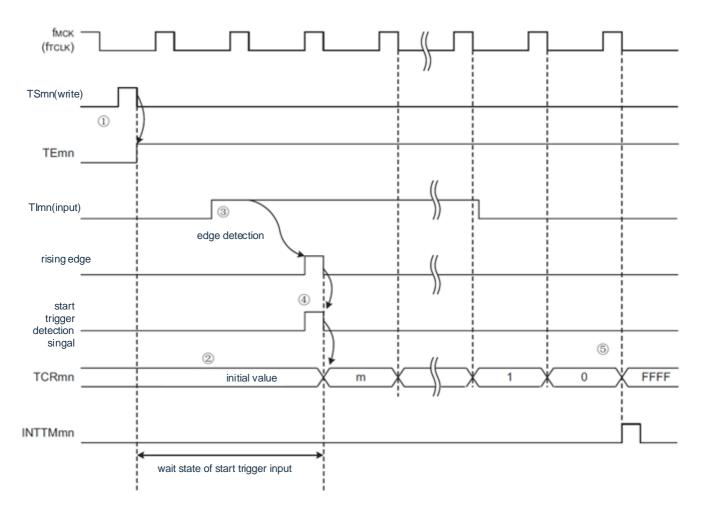

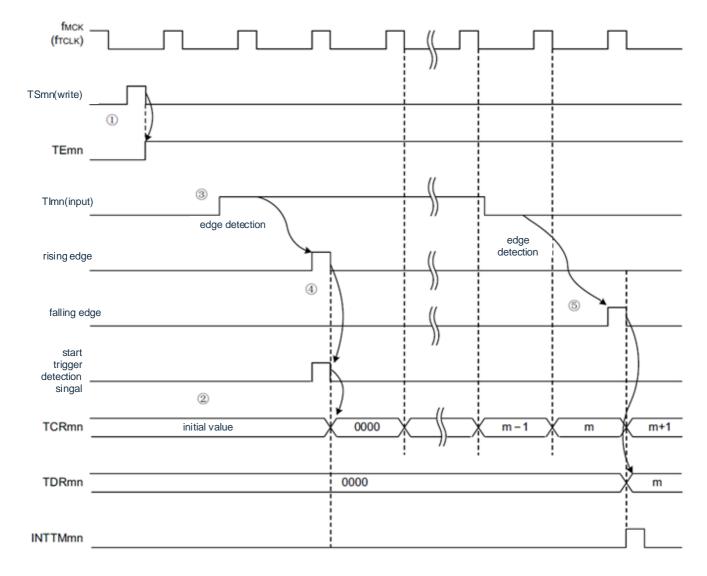

| 5.5 0   | Dperation of the counter                                                                  | 144       |

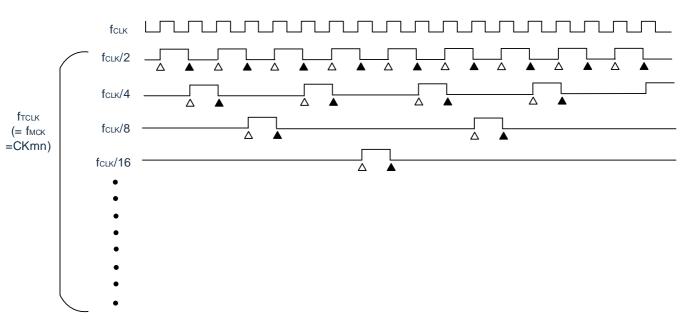

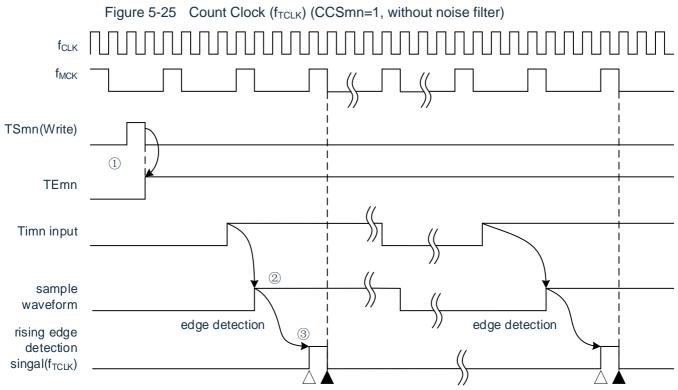

| 5.5.1   | Count clock (f <sub>TCLK</sub> )                                                          | 144       |

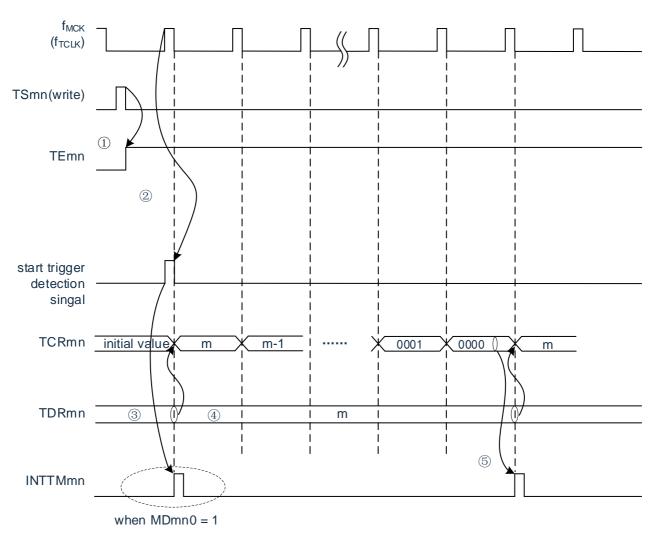

| 5.5.2   | Start timing of counter                                                                   | 146       |

| 5.5.3   |                                                                                           |           |

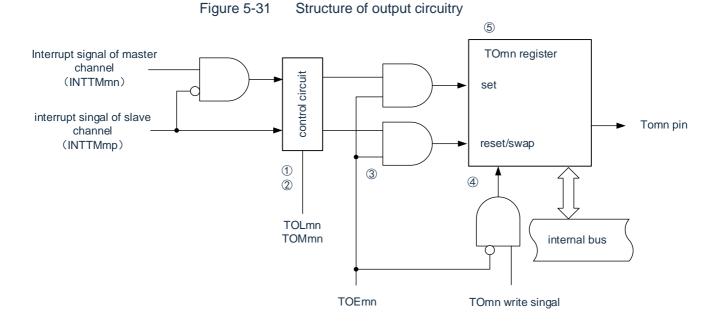

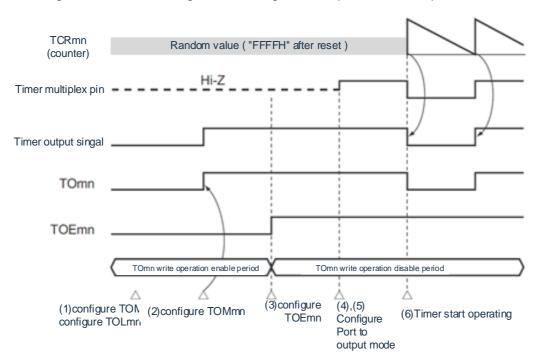

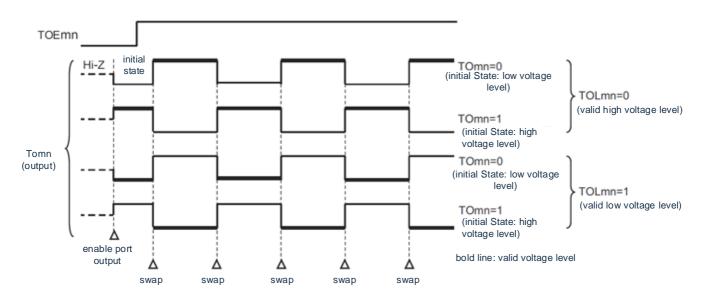

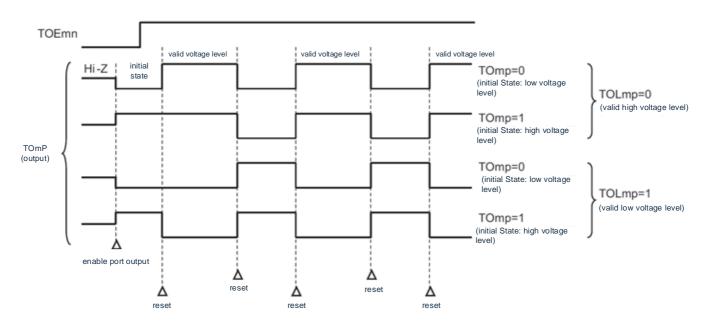

| 5.6 0   | Control of the channel output (TOmn pin)                                                  |           |

| 5.6.1   |                                                                                           |           |

| 5.6.2   |                                                                                           |           |

| 5.6.3   |                                                                                           |           |

| 5.6.4   |                                                                                           |           |

| 5.6.5   |                                                                                           |           |

|         | Control of timer input (TImn)                                                             |           |

| 5.7.1   |                                                                                           |           |

| 5.7.2   |                                                                                           |           |

| 5.7.3   |                                                                                           |           |

|         | ndependent channel operation function of the universal timer unit                         |           |

| 5.8.1   |                                                                                           |           |

| 5.8.2   |                                                                                           |           |

| 5.8.3   |                                                                                           |           |

| 5.8.4   |                                                                                           |           |

| 5.8.5   |                                                                                           |           |

| 5.8.6   |                                                                                           |           |

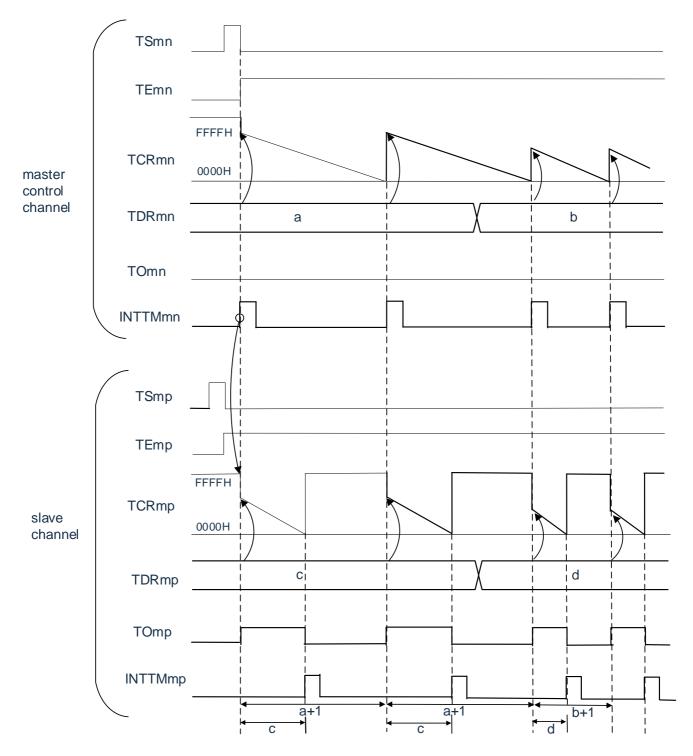

|         | fulti-channel linkage operation of the universal timer unit                               |           |

| 5.9.1   |                                                                                           |           |

| 5.9.2   |                                                                                           |           |

| 5.9.3   | •                                                                                         |           |

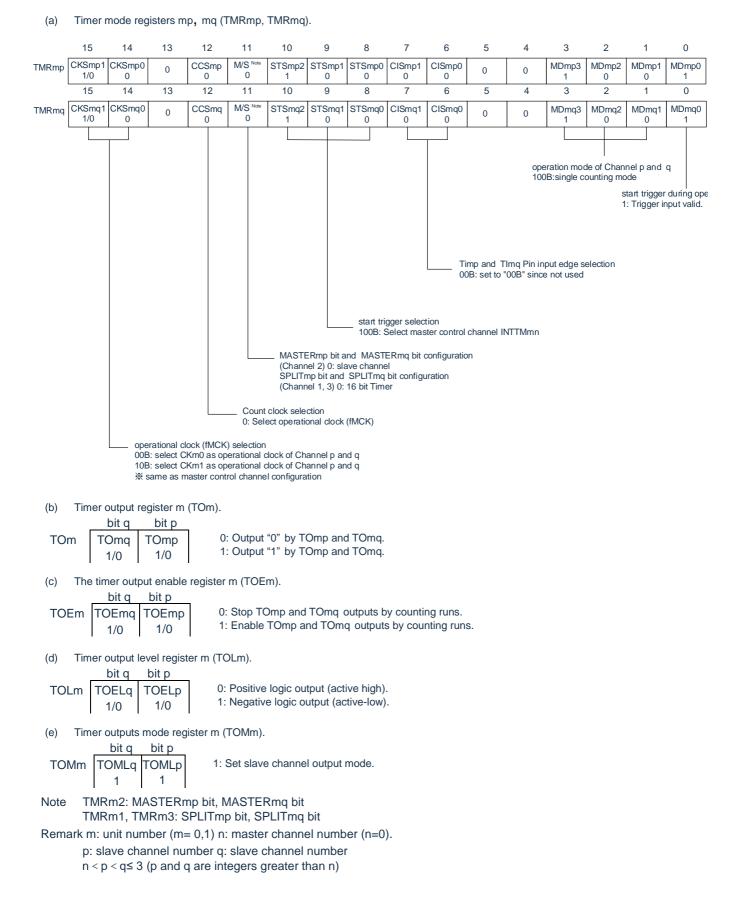

| Chapter |                                                                                           |           |

| -       |                                                                                           |           |

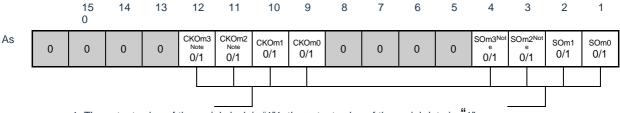

|         | Structure of the output control circuit                                                   |           |

|         | Registers for controlling EPWM output control circuit                                     |           |

| 6.2.1   | Peripheral enable register 1 (PER1)                                                       |           |

| 6.2.2   |                                                                                           |           |

| 6.2.3   |                                                                                           |           |

| 6.2.4   |                                                                                           |           |

| 6.2.5   |                                                                                           |           |

| 6.2.6   | 5 ( )                                                                                     |           |

| 6.2.7   | 5                                                                                         |           |

|         | Deration of EPWM output control circuit                                                   |           |

| 6.3.1   | Initial setup                                                                             |           |

| 6.3.2   |                                                                                           |           |

| 6.3.3   |                                                                                           |           |

|         | Control example of brushless DC motor                                                     |           |

| 6.4.1   | •                                                                                         |           |

| 6.4.2   | Control timing of three-phase brushless DC motors                                         | 215       |

Cmsemicon®

| 6.4.3     | Example of register setting                                                        | 216 |

|-----------|------------------------------------------------------------------------------------|-----|

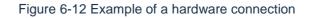

| 6.5 Exa   | mple of stepper motor control                                                      | 217 |

| 6.5.1     | Example of a hardware connection                                                   |     |

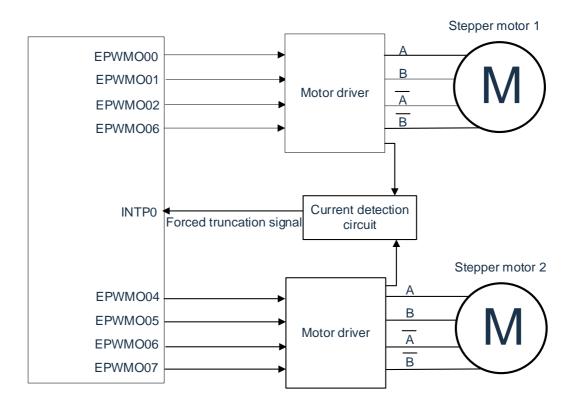

| 6.5.2     | Control method                                                                     | 218 |

| 6.5.3     | Example of register setting                                                        | 219 |

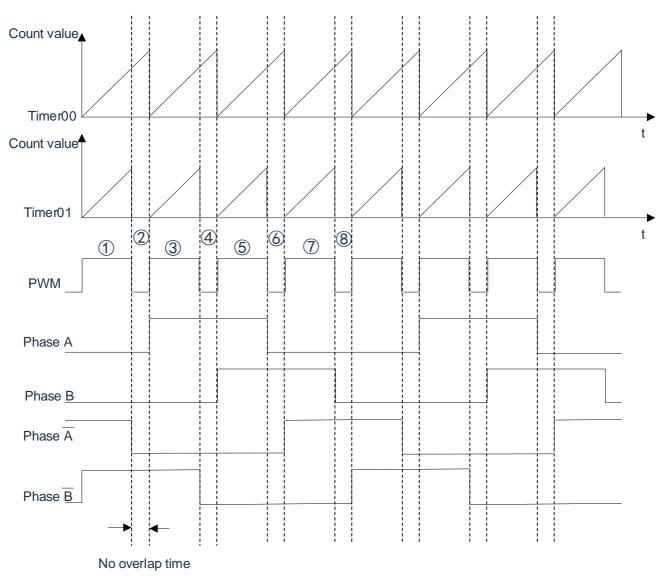

| Chapter 7 | Real-Time Clock                                                                    | 220 |

| 7.1 Fun   | ction of real-time clock                                                           | 220 |

|           | cture of real-time clock                                                           |     |

| 7.3 Reg   | isters for controlling real-time clock                                             |     |

| 7.3.1     | Peripheral enable register 0 (PER0)                                                |     |

| 7.3.2     | Real-time clock selection register (RTCCL)                                         | 224 |

| 7.3.3     | Real-time clock control register0 (RTCC0)                                          |     |

| 7.3.4     | Real-time clock control register1 (RTCC1)                                          | 226 |

| 7.3.5     | Clock error correction register (SUBCUD)                                           |     |

| 7.3.6     | Second count register (SEC)                                                        |     |

| 7.3.7     | Minute count register (MIN)                                                        | 229 |

| 7.3.8     | Hour count register (HOUR).                                                        | 230 |

| 7.3.9     | Day count register (DAY)                                                           | 232 |

| 7.3.10    | Week count Register (WEEK)                                                         | 233 |

| 7.3.11    | Month count register (MONTH)                                                       |     |

| 7.3.12    | Year Count Register (YEAR)                                                         | 234 |

| 7.3.13    | Alarm minute register (ALARMWM)                                                    | 235 |

| 7.3.14    | Alarm hour register (ALARMWH)                                                      | 235 |

| 7.3.15    | Alarm week register (ALARMWW)                                                      |     |

| 7.3.16    | Port mode register and port register                                               | 236 |

| 7.4 Ope   | eration of real-time clock                                                         | 237 |

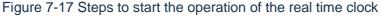

| 7.4.1     | Start of real-time clock operation                                                 |     |

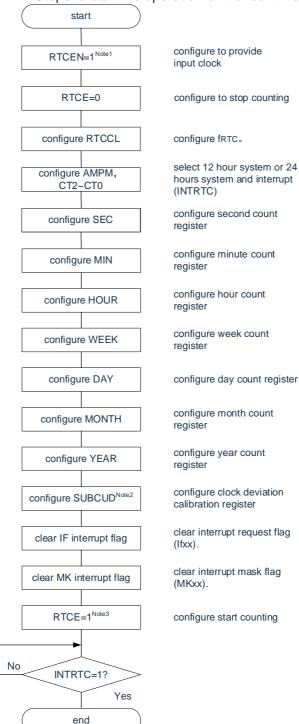

| 7.4.2     | Shifting to sleep mode after starting operation                                    |     |

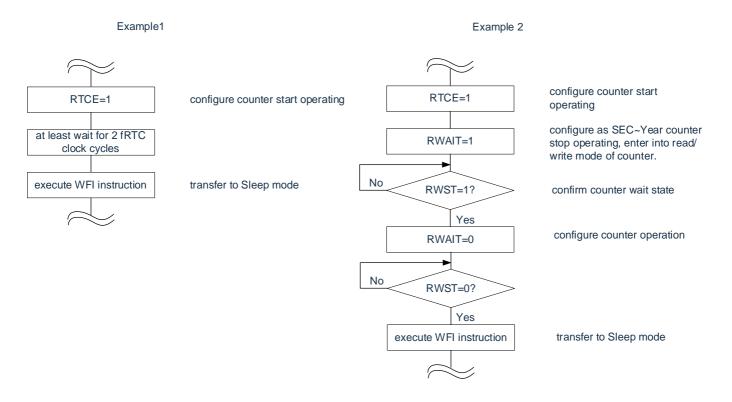

| 7.4.3     | Read and write to the real-time clock counter                                      |     |

| 7.4.4     | Alarm setting for real-time clock                                                  | 241 |

| 7.4.5     | 1Hz output of the real-time clock                                                  |     |

| 7.4.6     | Example of clock error correction for a real-time clock                            | 243 |

| Chapter 8 | 15-Bit Interval Timer                                                              | 245 |

| 8.1 Fun   | ction of 15-bit interval timer                                                     | 245 |

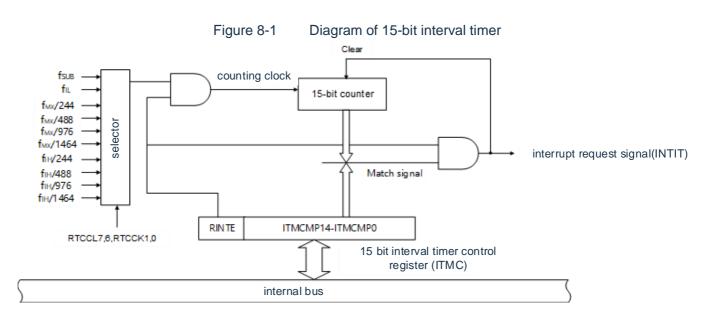

| 8.2 Stru  | cture of 15-bit interval timer                                                     | 245 |

| 8.3 Reg   | isters for controlling 15-bit interval timer                                       | 246 |

| 8.3.1     | Peripheral enable register 0 (PER0)                                                | 246 |

| 8.3.2     | Real-time clock selection register (RTCCL)                                         | 247 |

| 8.3.3     | 15-bit interval timer control register (ITMC)                                      | 248 |

| 8.4 15-1  | pit interval timer operation                                                       | 249 |

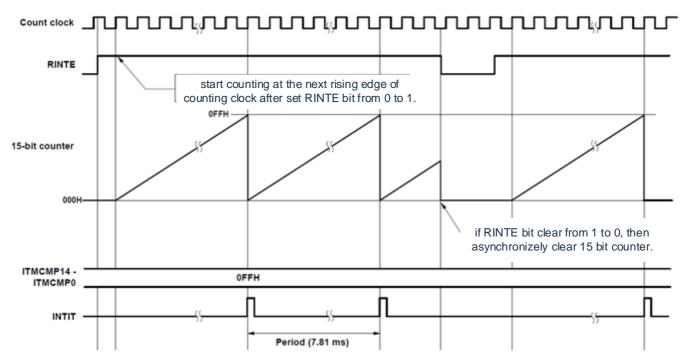

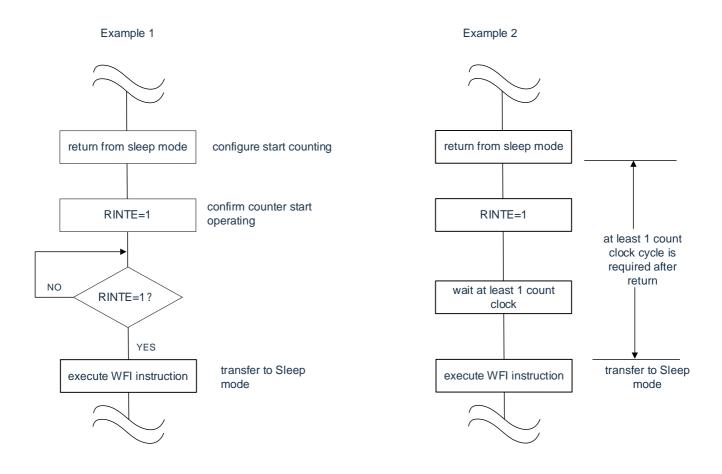

| 8.4.1     | 15-bit interval timer operation timing                                             | 249 |

| 8.4.2     | Start of count operation and re-enter to sleep mode after returned from sleep mode | 250 |

| Chapter 9 | Clock output/Buzzer Output Controller                                              | 251 |

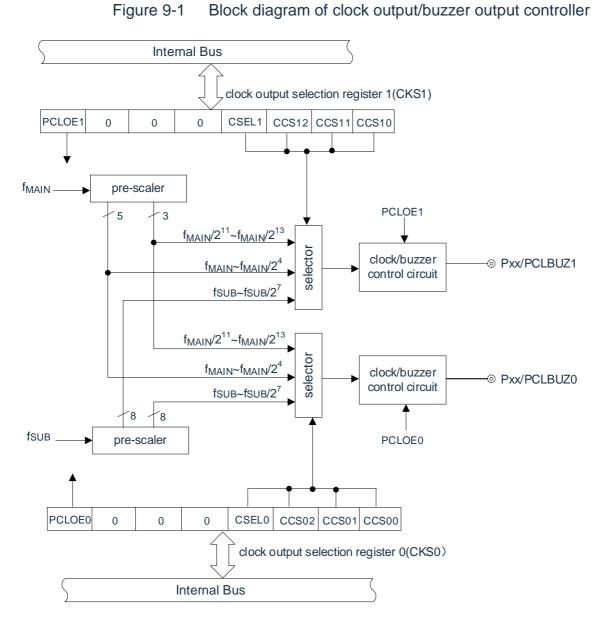

| 9.1 Fun   | ctions of clock output/buzzer output controller                                    | 251 |

|           | cture of clock output/buzzer output controller                                     |     |

|           | isters for controlling clock output/buzzer output controller                       |     |

| 9.3.1      | Clock output select register n (CKSn)                                             | 253 |

|------------|-----------------------------------------------------------------------------------|-----|

| 9.3.2      | Registers for controlling the function of the clock output/buzzer output pin port | 255 |

| 9.4 Ope    | ration of clock output/buzzer controller                                          | 256 |

| 9.4.1      | Operation of output pin                                                           | 256 |

| 9.5 Cau    | tions for clock output/buzzer output control circuitry                            | 256 |

| Chapter 10 | ) Watchdog Timer                                                                  | 257 |

| 10.1 Fund  | ction of watchdog timer                                                           | 257 |

| 10.2 Stru  | cture of watchdog timer                                                           | 257 |

| 10.3 Reg   | isters for controlling watchdog timer                                             | 259 |

| 10.3.1     | Watchdog timer enable register (WDTE)                                             | 259 |

| 10.3.2     | LOCKUP control register (LOCKCTL)and its protection register (PRCR)               |     |

| 10.4 Ope   | ration of the watchdog timer                                                      | 261 |

| 10.4.1     | Operational control of the watchdog timer                                         | 261 |

| 10.4.2     | Watchdog timer overflow time setting                                              | 262 |

| 10.4.3     | Setting window open period of watchdog timer                                      | 263 |

| 10.4.4     | Setting watchdog timer interval interruption                                      | 264 |

| 10.4.5     | Operation of the watchdog timer during LOCKUP                                     | 264 |

| Chapter 11 | A/D Converter                                                                     | 265 |

| 11.1 Fund  | ction of A/D converter                                                            |     |

| 11.2 Con   | trol registers of A/D converter                                                   |     |

| 11.2.1     | Peripheral enable register 0 (PER0)                                               |     |

| 11.2.2     | A/D converter mode register 0 (ADM0)                                              |     |

| 11.2.3     | A/D converter mode register 1 (ADM1)                                              | 274 |

| 11.2.4     | A/D converter mode register 2 (ADM2)                                              | 275 |

| 11.2.5     | A/D converter trigger mode register (ADTRG)                                       |     |

| 11.2.6     | Analog input channel specification register (ADS)                                 | 277 |

| 11.2.7     | 12-bit A/D conversion result register (ADCR)                                      | 279 |

| 11.2.8     | 8-bit A/D conversion result register (ADCRI)                                      |     |

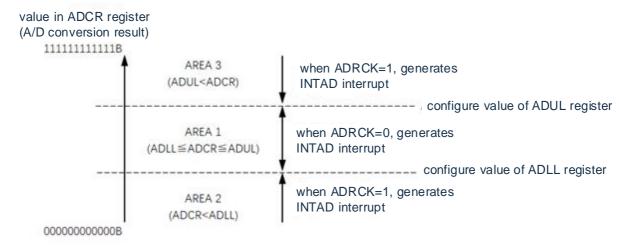

| 11.2.9     | Conversion result comparison upper limit setting register (ADUL)                  |     |

| 11.2.10    | Conversion result comparison lower limit setting register (ADLL)                  |     |

| 11.2.11    | A/D converter sampling time extension control register (ADSMPWAIT)                |     |

| 11.2.12    | Registers for controlling the function of the analog input pin port               |     |

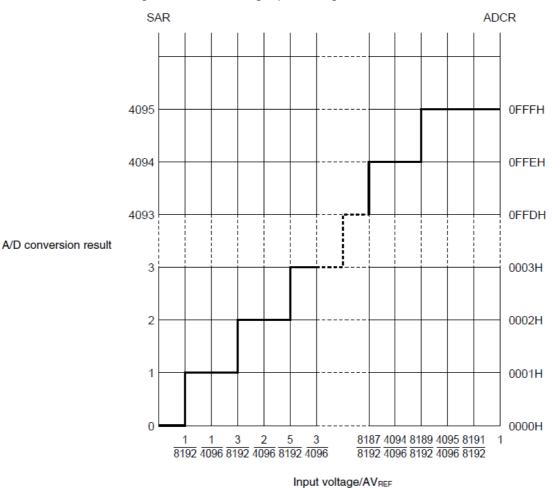

| 11.3 Inpu  | t voltage and conversion results                                                  |     |

| 11.4 Ope   | ration mode of A/D converter                                                      |     |

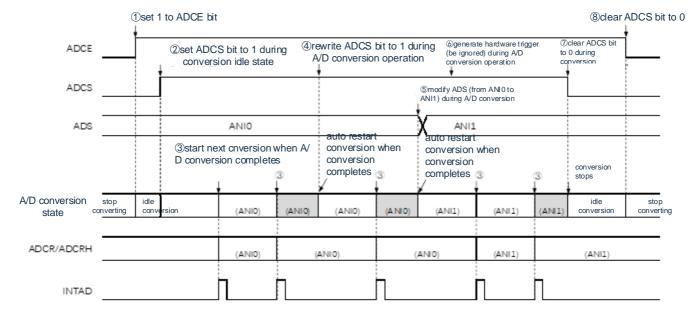

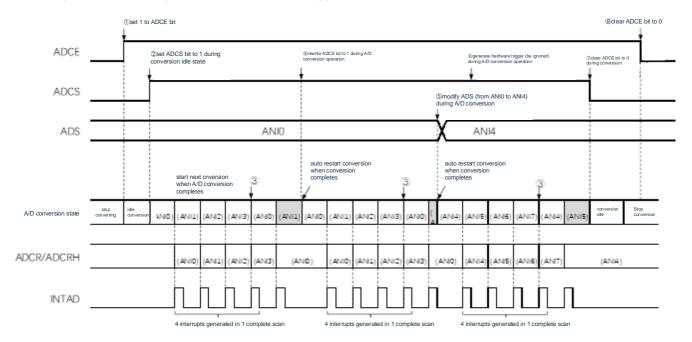

| 11.4.1     | Software trigger mode (select mode, continuous conversion mode)                   |     |

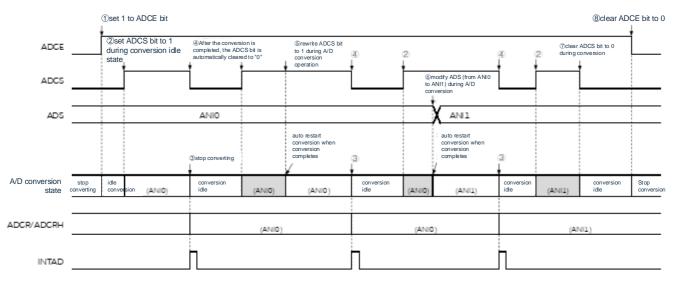

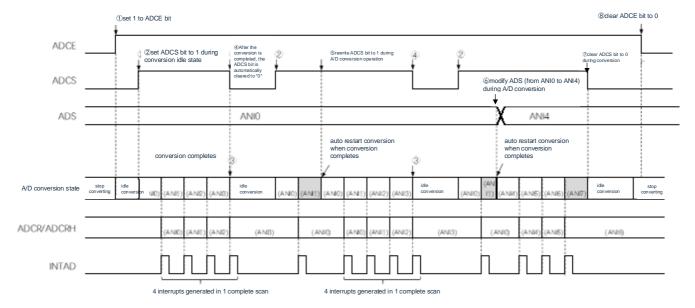

| 11.4.2     | Software trigger mode (select mode, single conversion mode)                       |     |

| 11.4.3     | Software trigger mode (scan mode, continuous conversion mode)                     |     |

| 11.4.4     | Software trigger mode (scan mode, single conversion mode)                         |     |

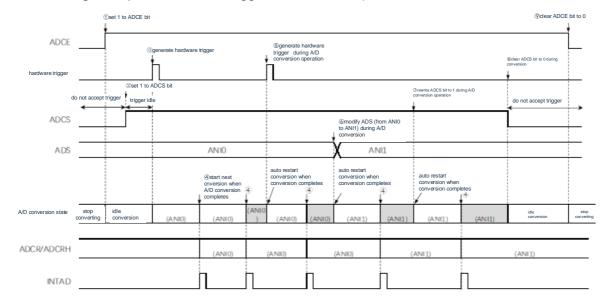

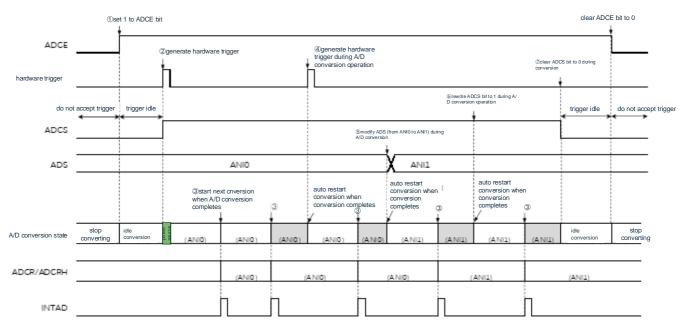

| 11.4.5     | Hardware triggered no-wait mode (select mode, continuous conversion mode)         |     |

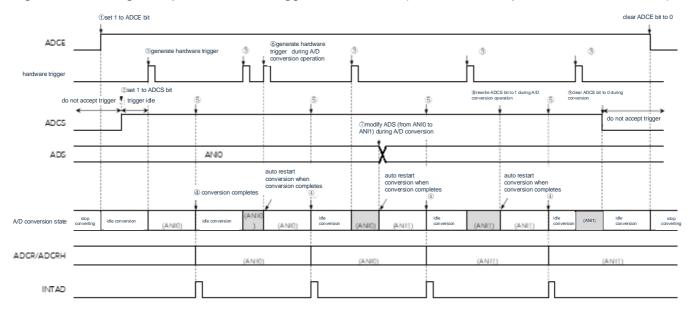

| 11.4.6     | Hardware trigger no-wait mode (select mode, single conversion mode)               |     |

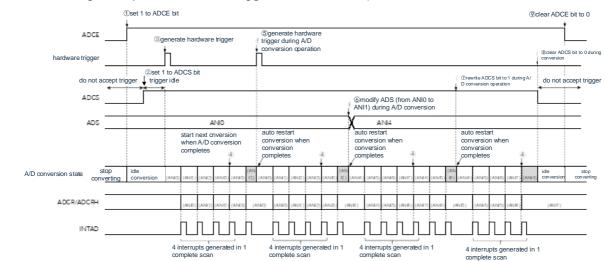

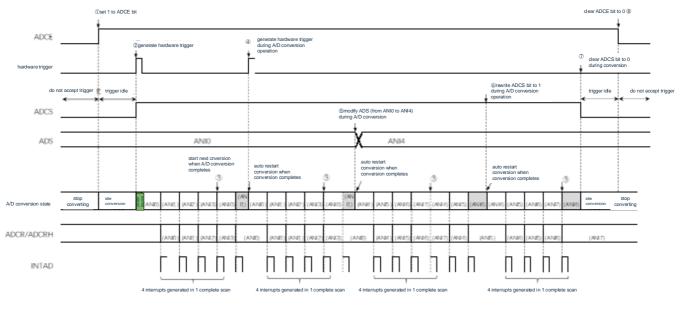

| 11.4.7     | Hardware trigger no-wait mode (scan mode, continuous conversion mode)             |     |

| 11.4.8     | Hardware trigger no-wait mode (scan mode, single conversion mode)                 |     |

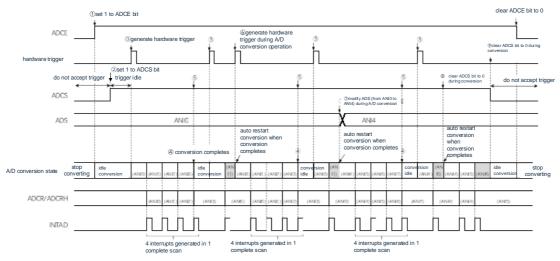

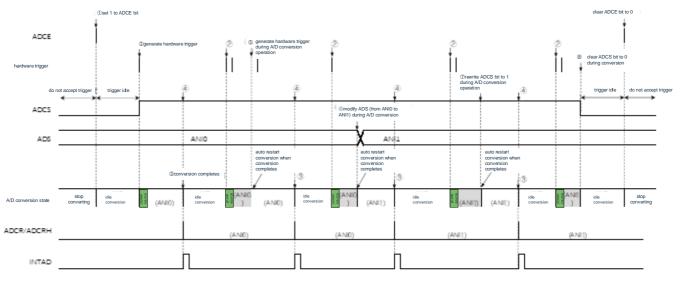

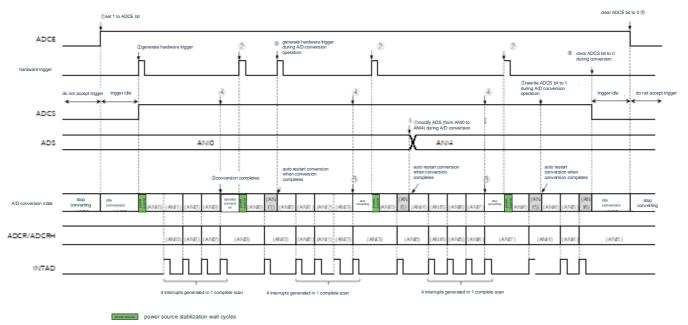

| 11.4.9     | Hardware trigger wait mode (select mode, continuous conversion mode)              | 291 |

| 11.4.10    | Hardware trigger wait mode (select mode, single conversion mode)                  | 292 |

| 11.4.11    | Hardware trigger wait mode (scan mode, continuous conversion mode)                | 293 |

| 11.4.12    | Hardware trigger wait mode (scan mode, single conversion mode)                    | 294 |

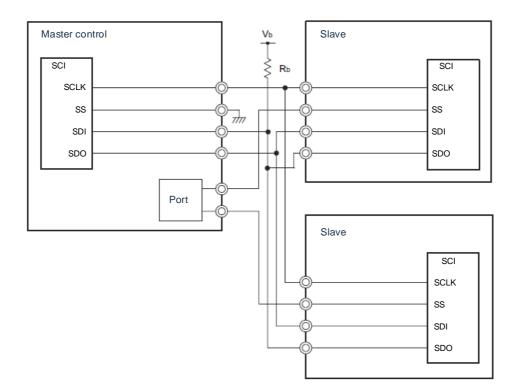

| Chapter 12        | 2 Universal Serial Communication Unit                                                                | 295 |

|-------------------|------------------------------------------------------------------------------------------------------|-----|

| 12.1 Fund         | ction of universal serial communication unit                                                         |     |

| 12.1.1            | 3-wire serial I/O (SSPI00, SSPI01, SSPI10, SSPI11, SSPI20, SSPI21)                                   |     |

| 12.1.2            | UART (UART0~UART2)                                                                                   |     |

| 12.1.3            | Simple I <sup>2</sup> C (IIC00, IIC01, IIC10, IIC11, IIC20, IIC21)                                   |     |

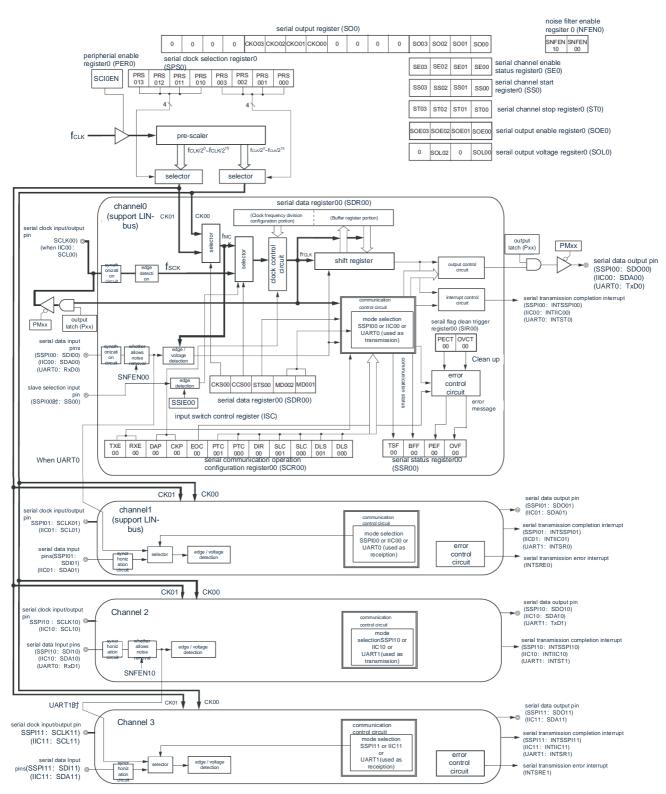

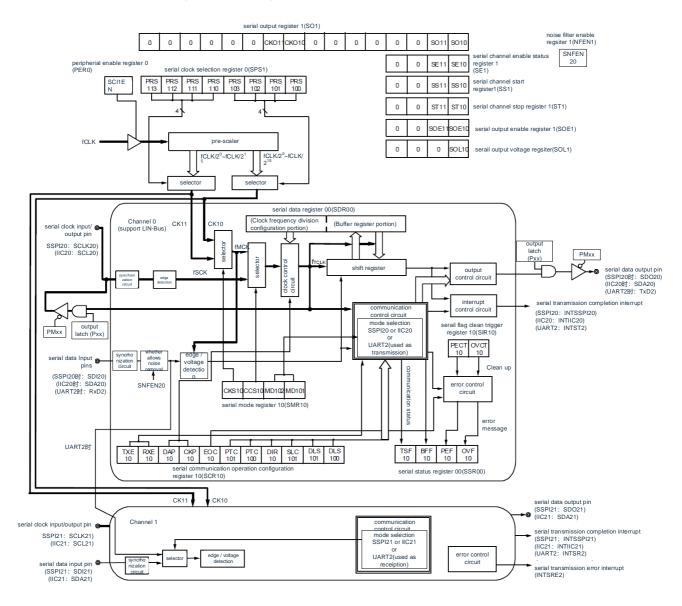

| 12.2 Strue        | cture of universal serial communication unit                                                         | 299 |

| 12.2.1            | Shift register                                                                                       |     |

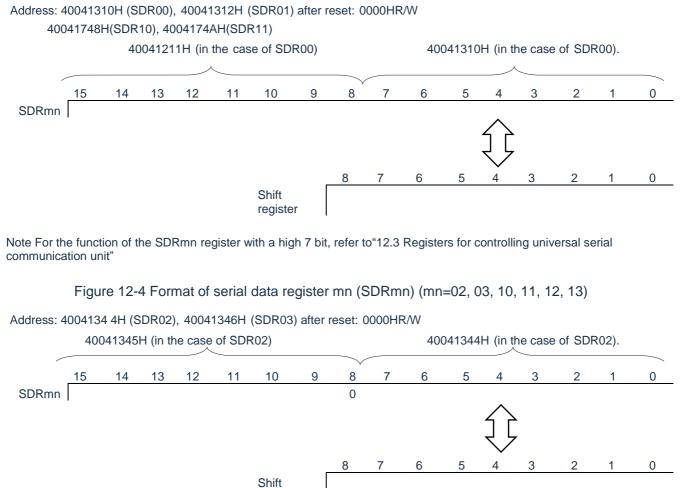

| 12.2.2            | Low 8 bits or low 9 bits of serial data register mn (SDRmn)                                          |     |

| 12.3 Regi         | sters for controlling universal serial communication unit                                            | 304 |

| 12.3.1            | Peripheral enable register 0 (PER0)                                                                  | 305 |

| 12.3.2            | Serial clock select register m (SPSm)                                                                |     |

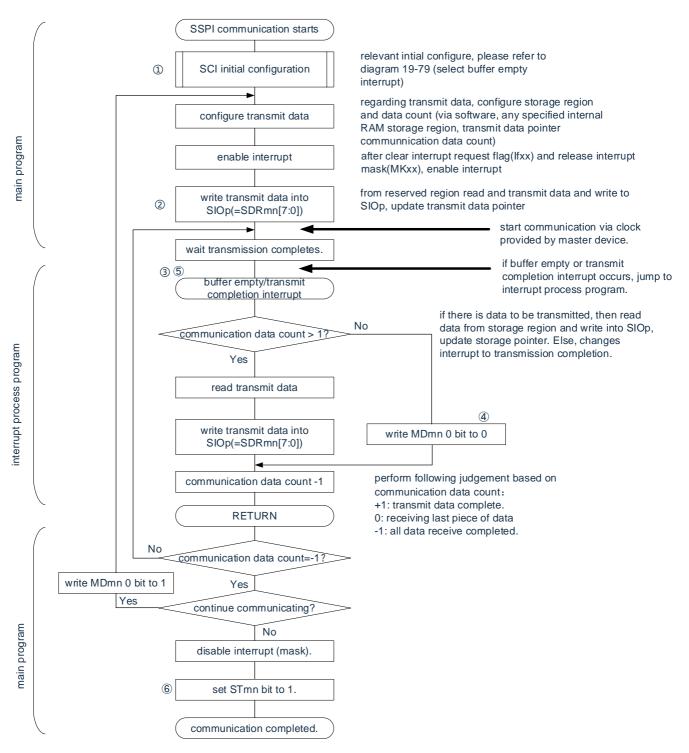

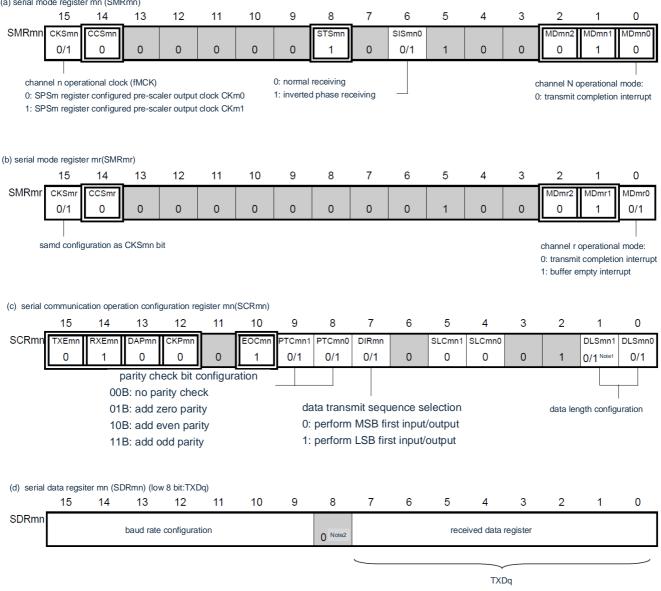

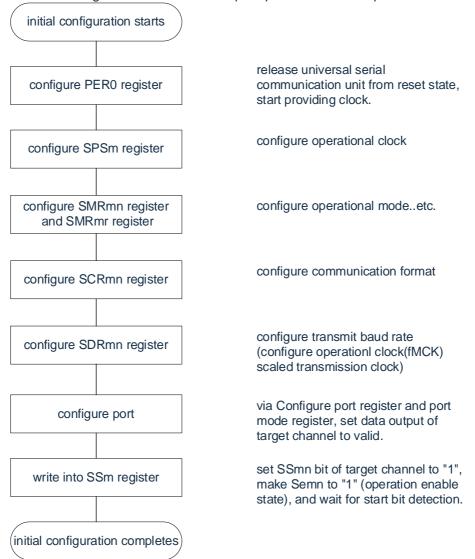

| 12.3.3            | Serial mode register mn (SMRmn)                                                                      | 307 |

| 12.3.4            | Serial communication operation setting register mn (SCRmn)                                           |     |

| 12.3.5            | Serial data register mn (SDRmn).                                                                     | 311 |

| 12.3.6            | Serial flag clear trigger register mn (SIRmn)                                                        | 313 |

| 12.3.7            | Serial status register mn (SSRmn)                                                                    | 314 |

| 12.3.8            | Serial channel start register m (SSm)                                                                | 316 |

| 12.3.9            | Serial channel stop register m (STm)                                                                 | 317 |

| 12.3.10           | Serial channel enable status register m (SEm)                                                        | 318 |

| 12.3.11           | Serial output enable register m(SOEm)                                                                | 319 |

| 12.3.12           | Serial output register m (SOm)                                                                       | 320 |

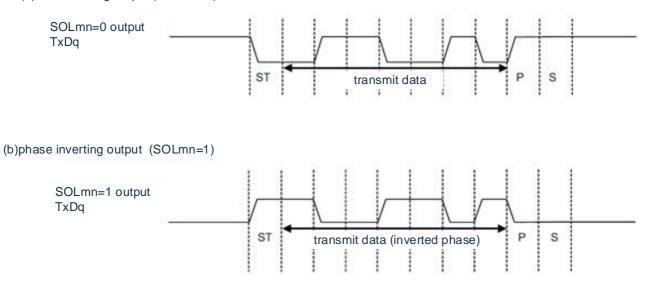

| 12.3.13           | Serial output level register m (SOLm)                                                                | 321 |

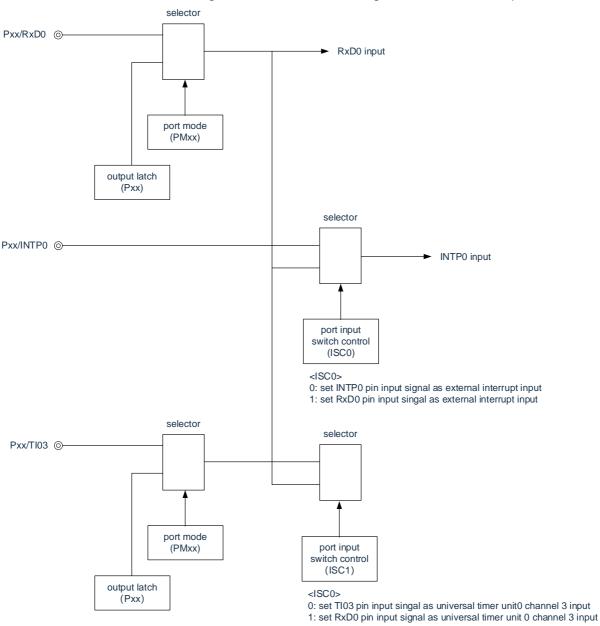

| 12.3.14           | Input switching control register (ISC)                                                               | 323 |

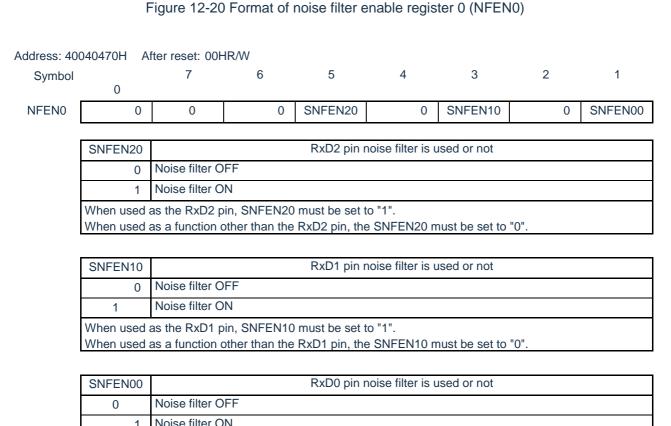

| 12.3.15           | Noise filter enable register 0 (NFEN0)                                                               | 324 |

| 12.3.16           | Registers controlling the function of the serial input/output pin port                               | 325 |

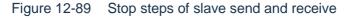

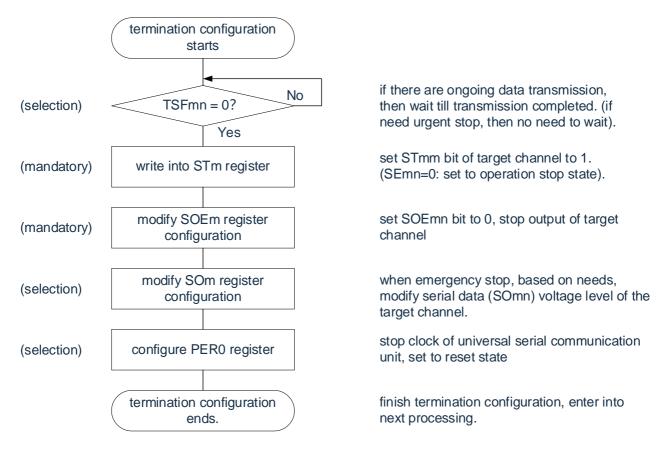

| 12.4 Ope          | ration stop mode                                                                                     | 326 |

| 12.4.1            | Stopping the operation by units                                                                      | 326 |

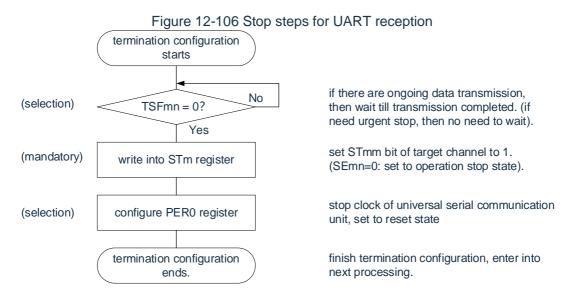

| 12.4.2            | Stopping the operation by channels                                                                   | 327 |

| 12.5 3-wii        | re serial I/O (SSPI00, SSPI01, SSPI10, SSPI11, SSPI20, SSPI21) communication                         | 328 |

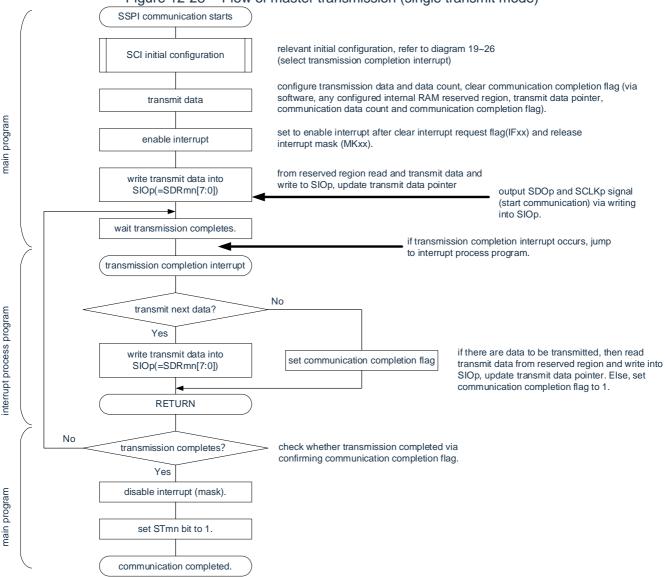

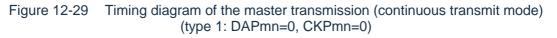

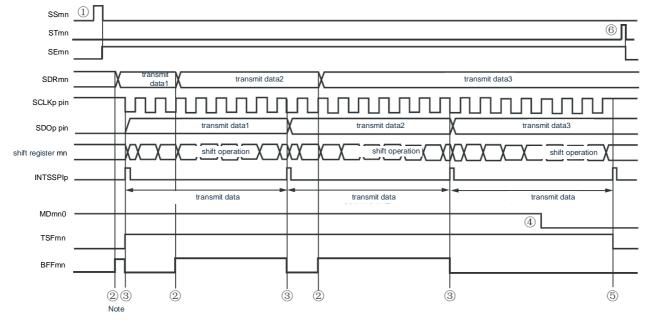

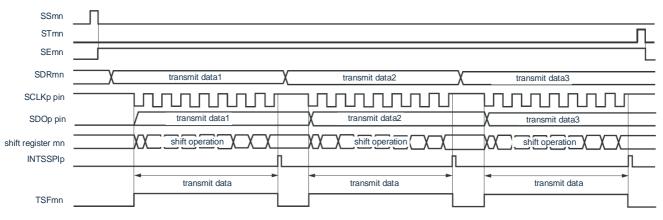

| 12.5.1            | Master transmission                                                                                  | 329 |

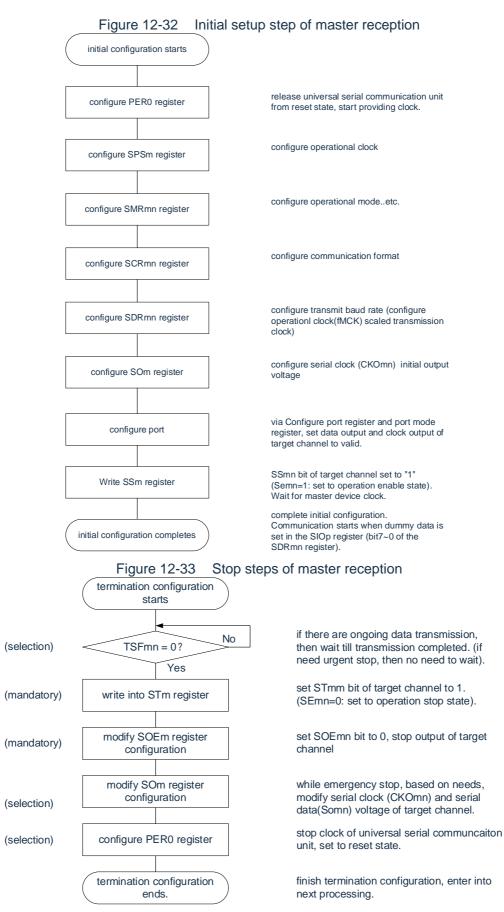

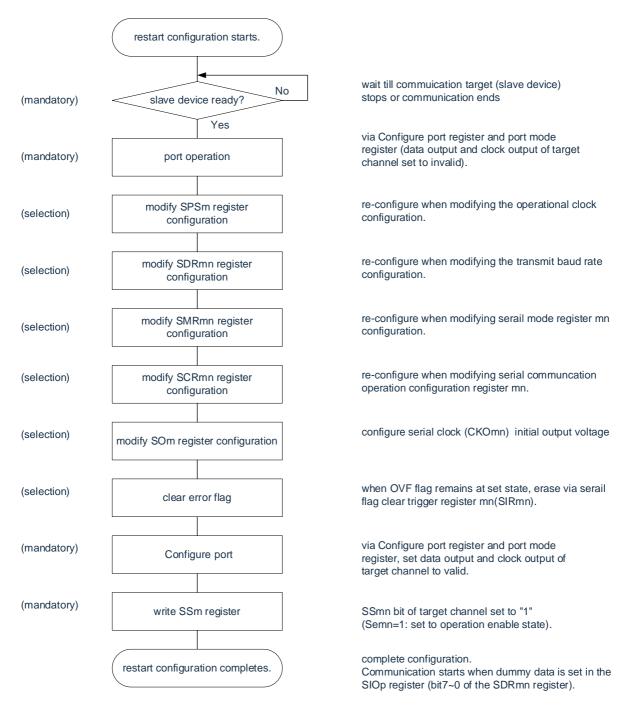

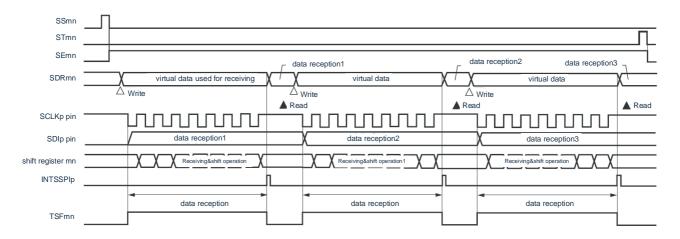

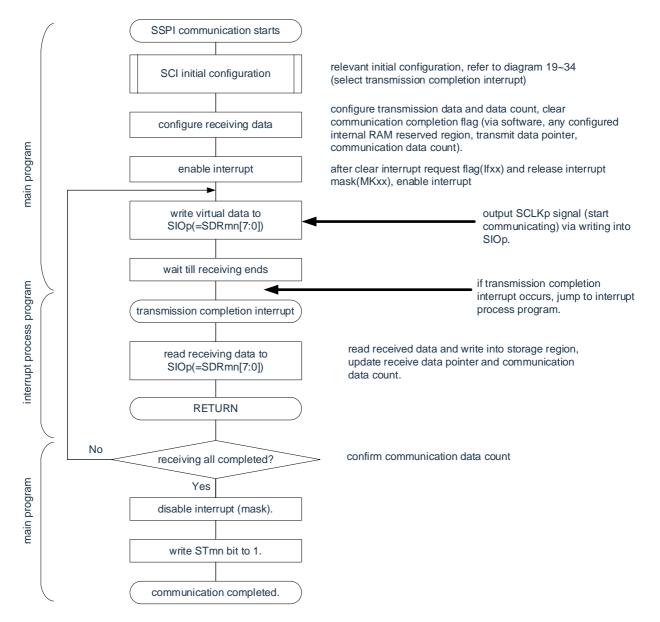

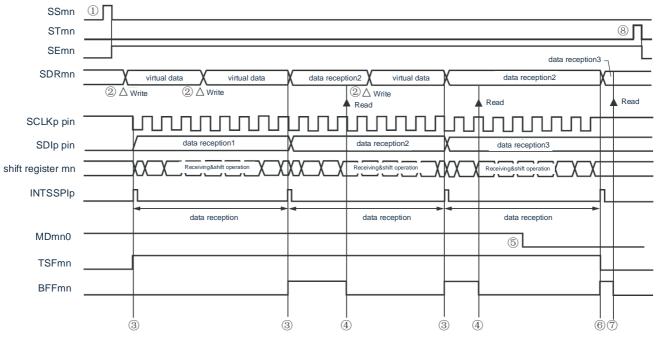

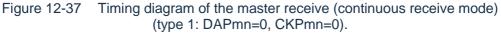

| 12.5.2            | Master reception                                                                                     | 338 |

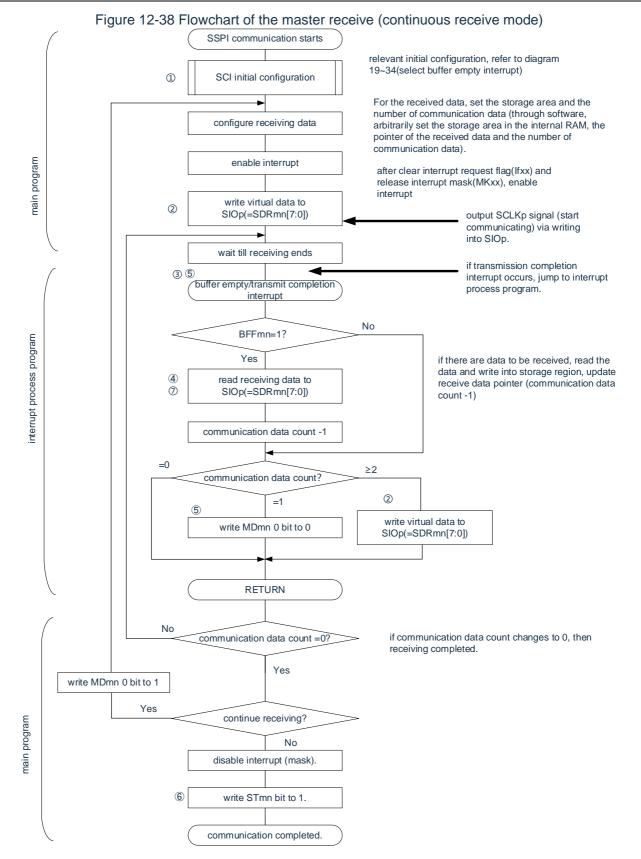

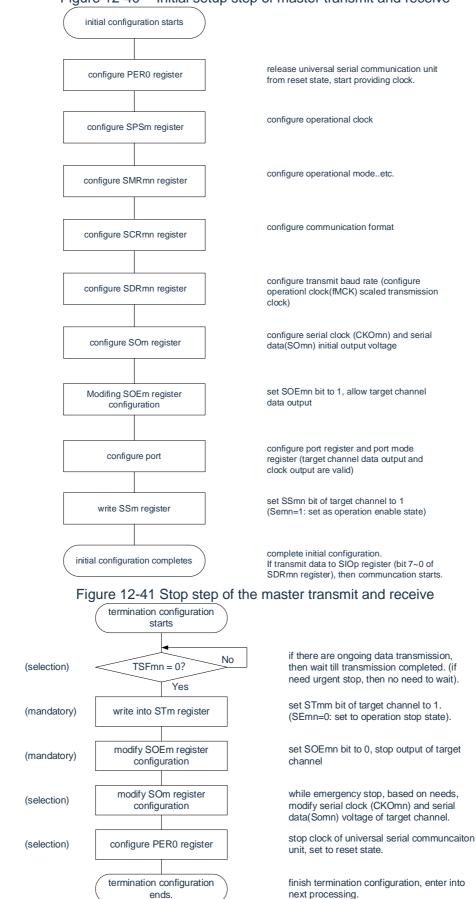

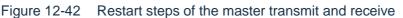

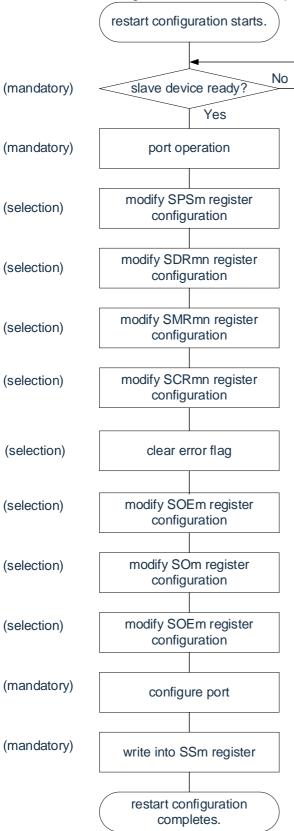

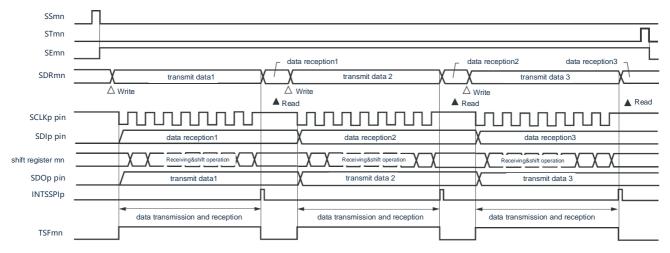

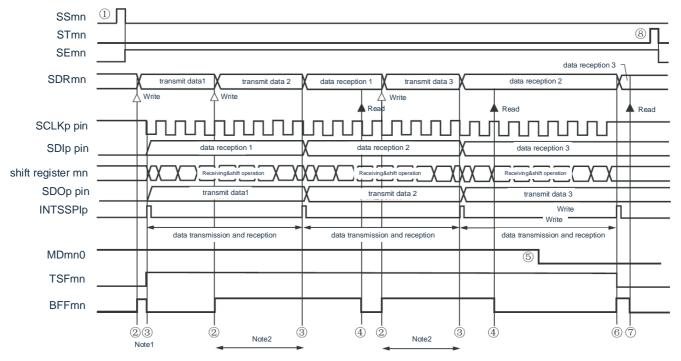

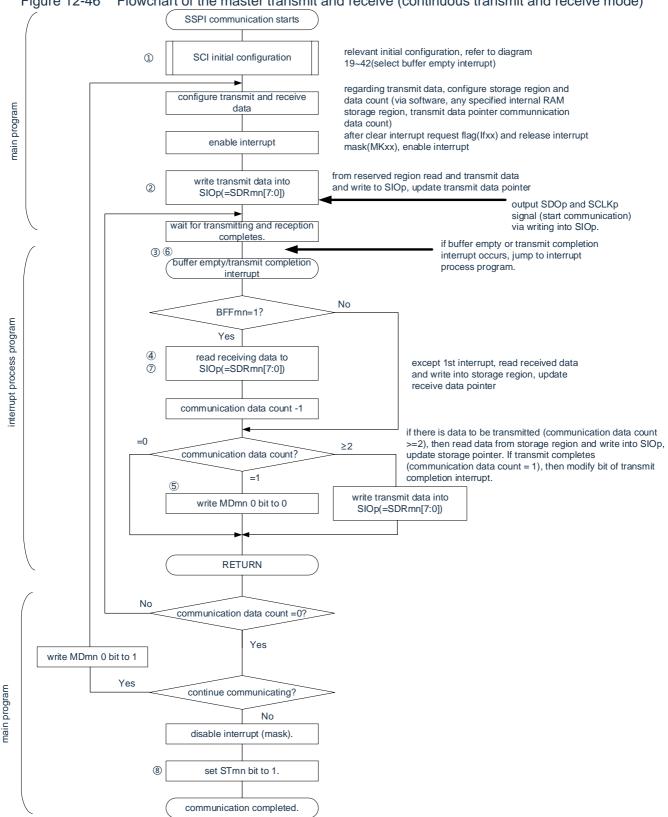

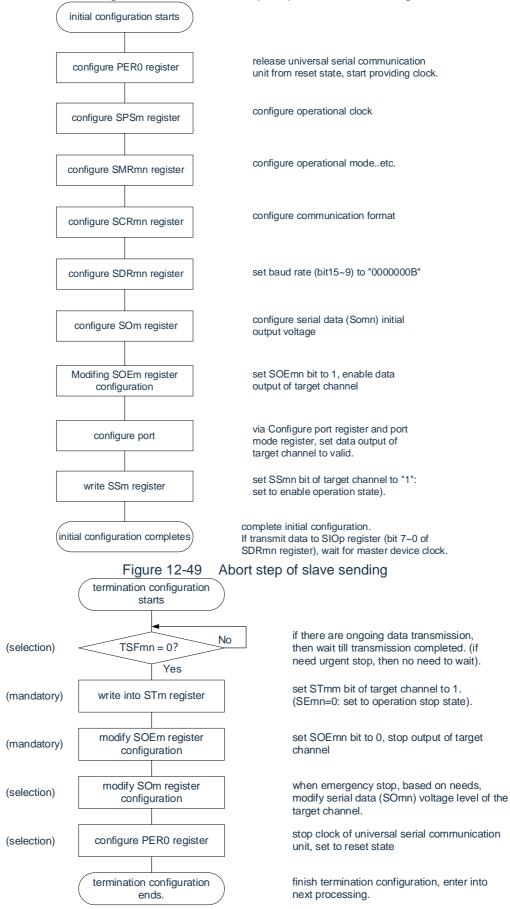

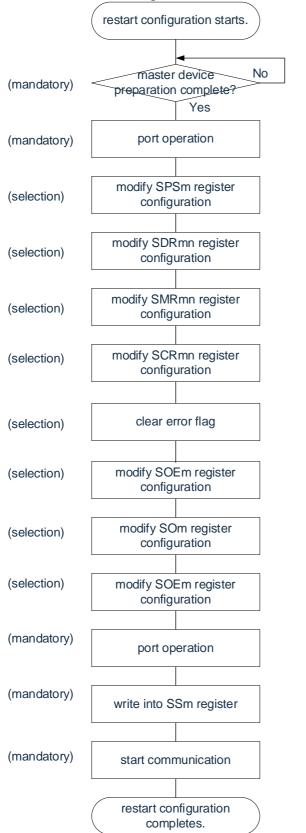

| 12.5.3            | Master transmission and reception                                                                    | 346 |

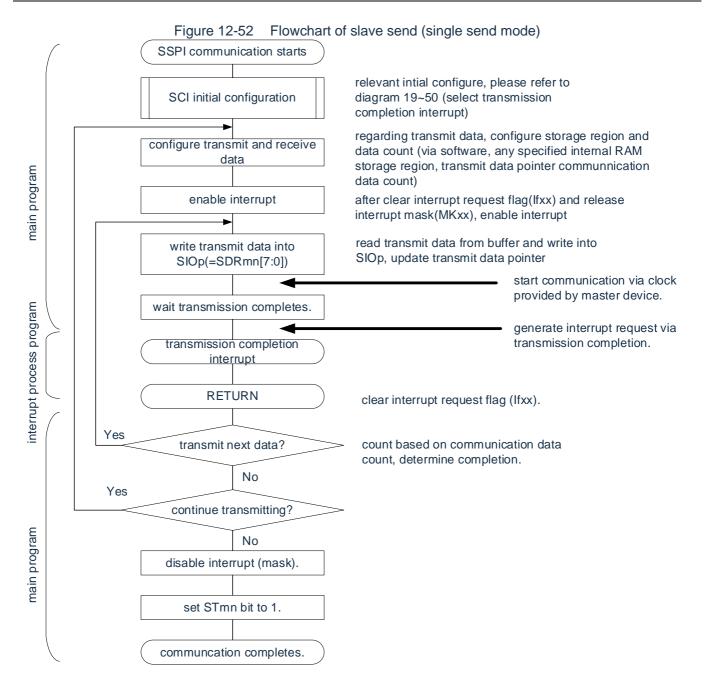

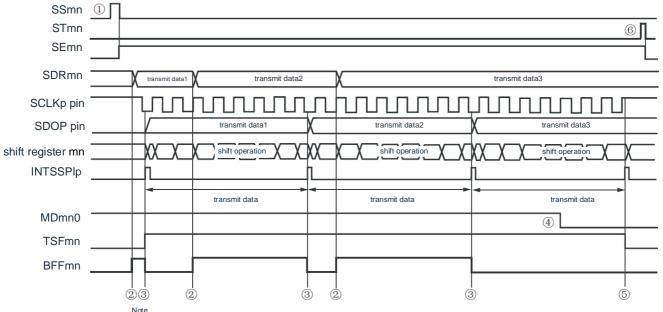

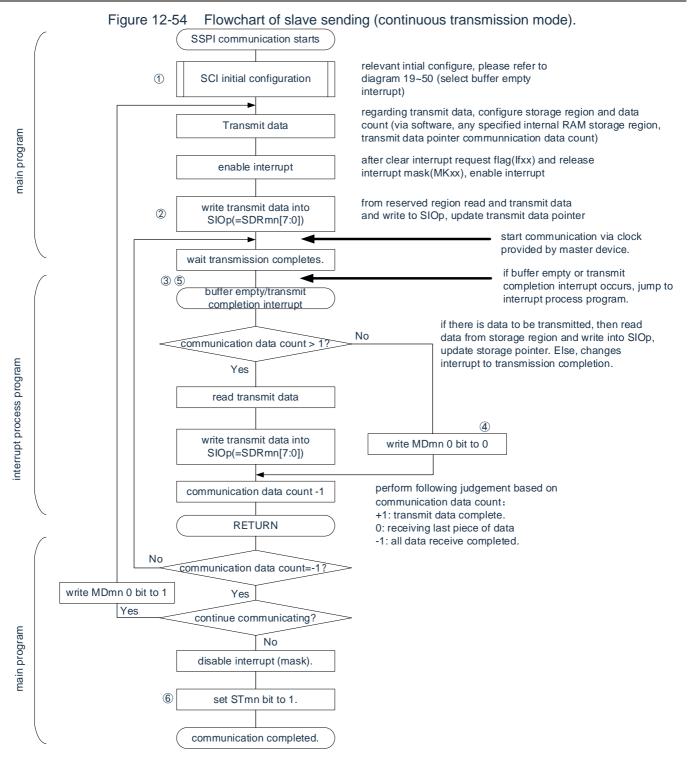

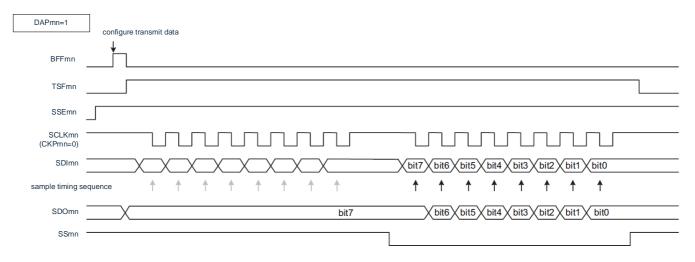

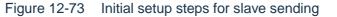

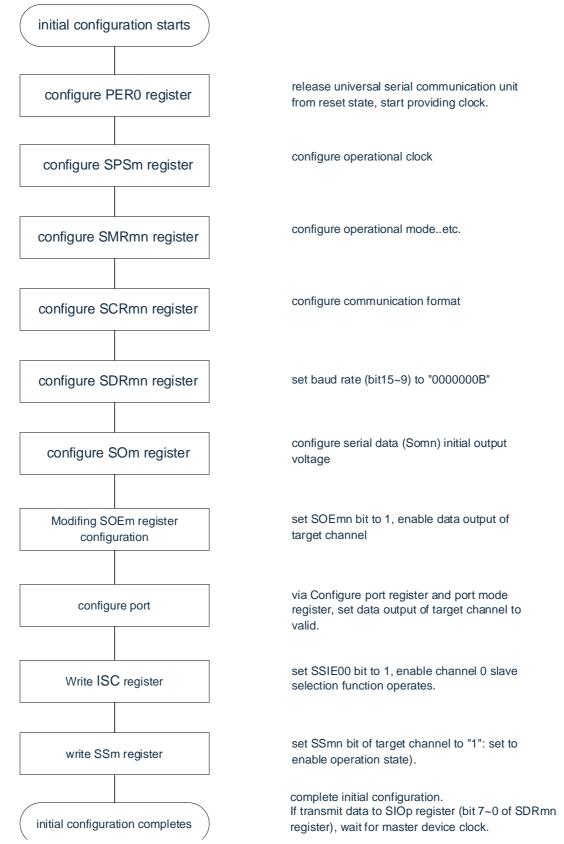

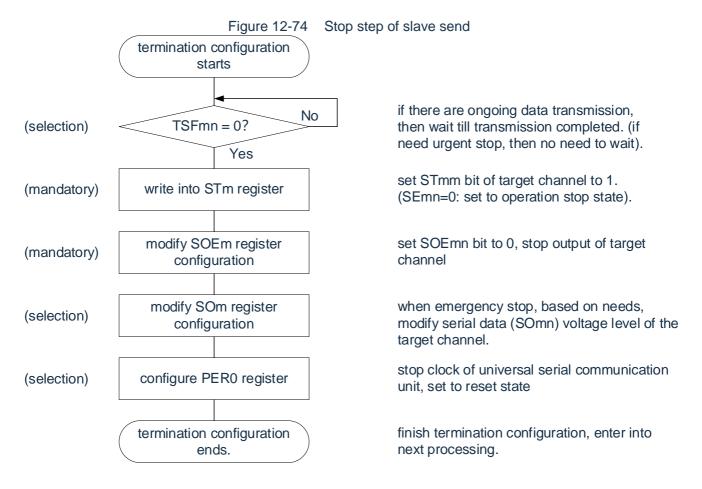

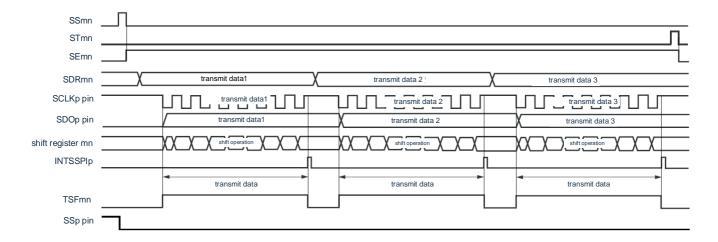

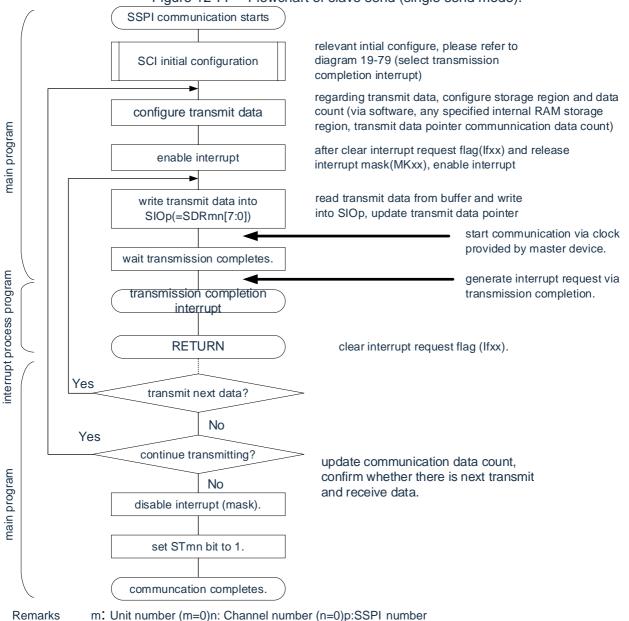

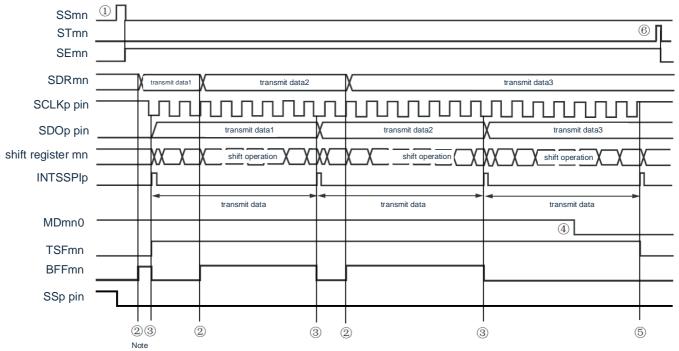

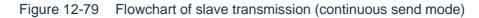

| 12.5.4            | Slave transmission                                                                                   | 354 |

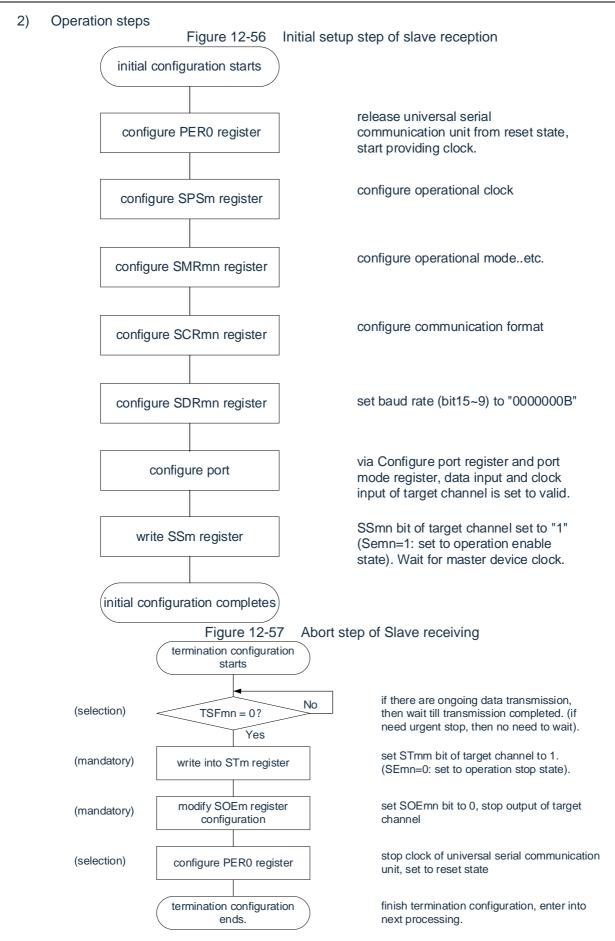

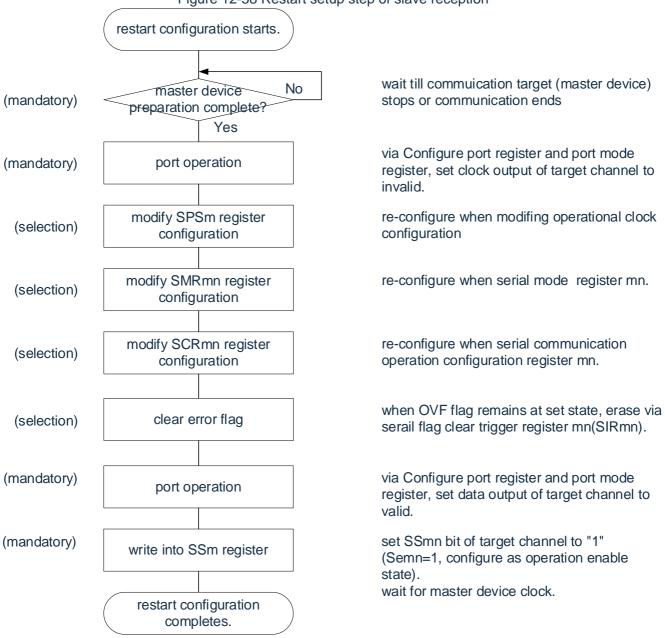

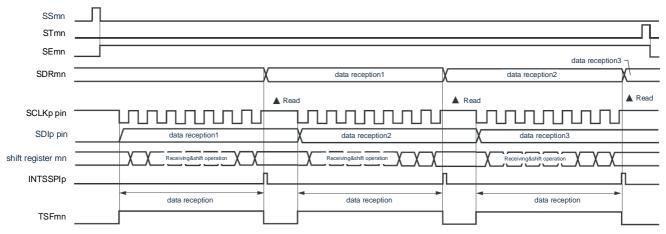

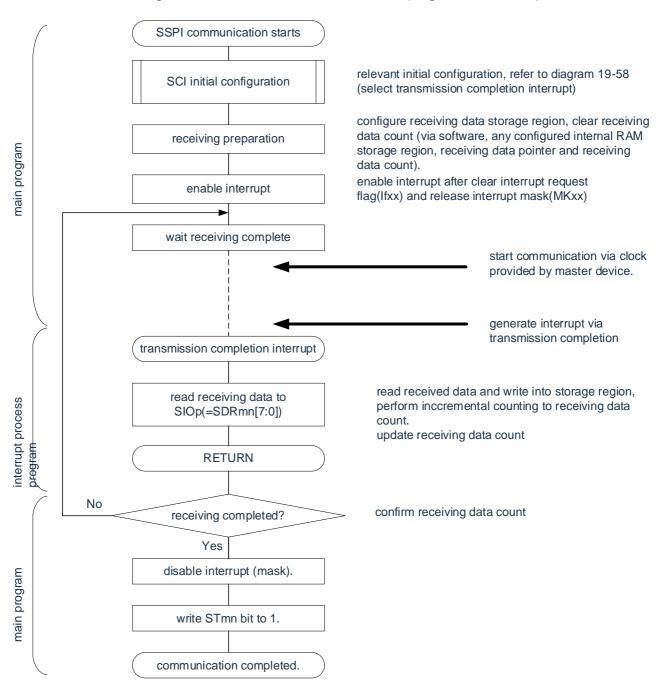

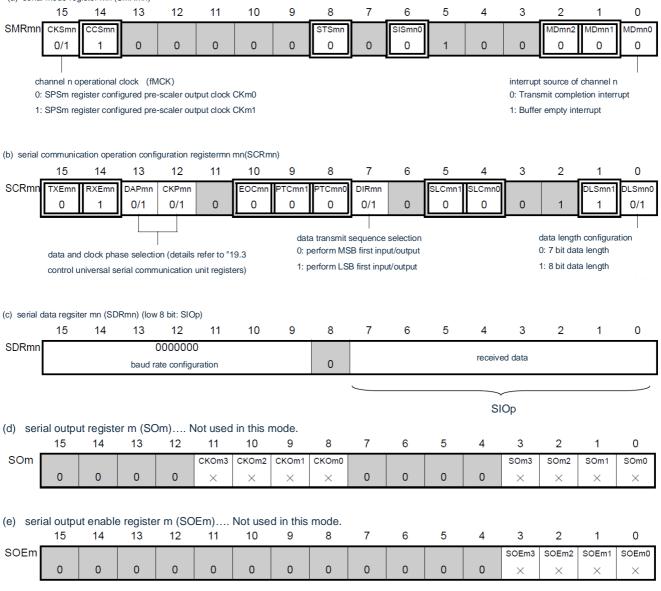

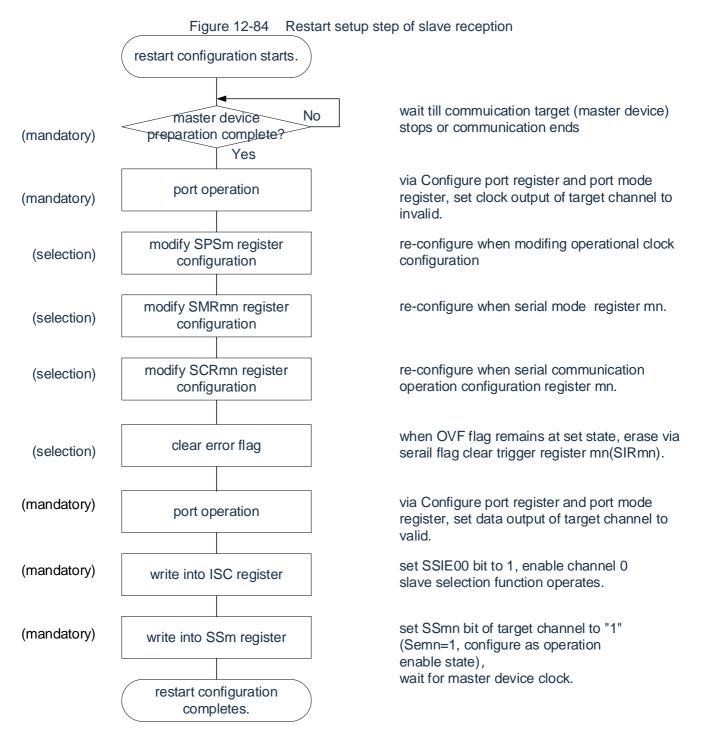

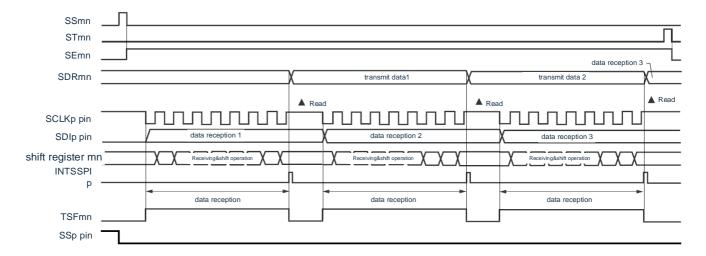

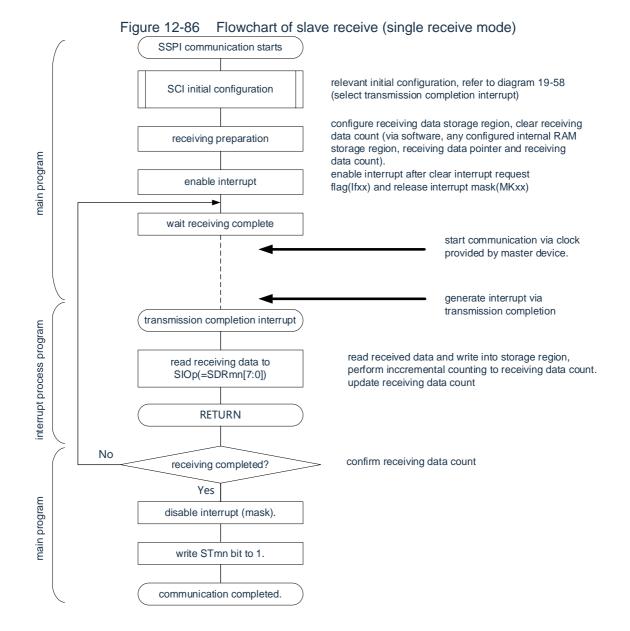

| 12.5.5            | Slave receiving                                                                                      | 362 |

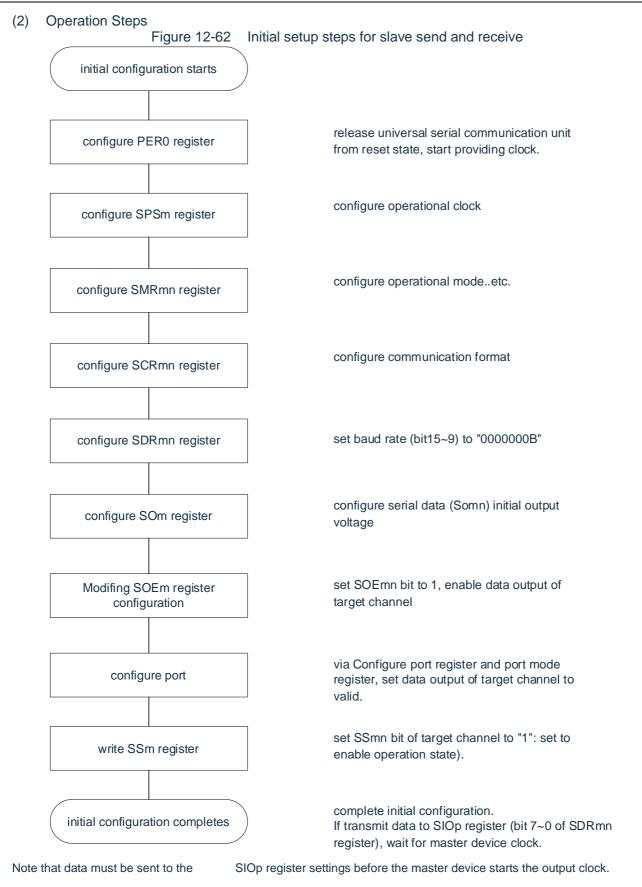

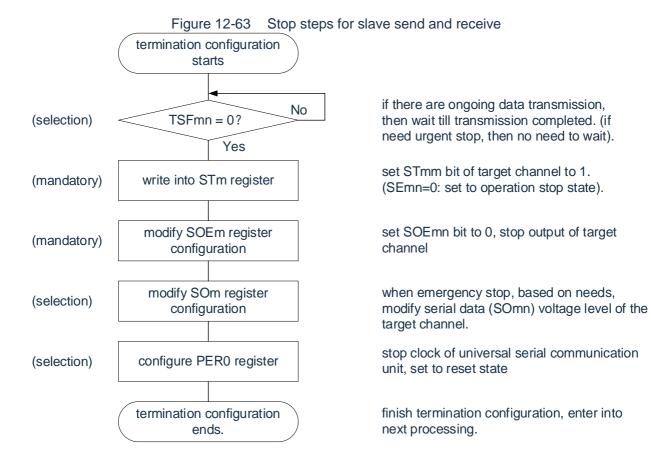

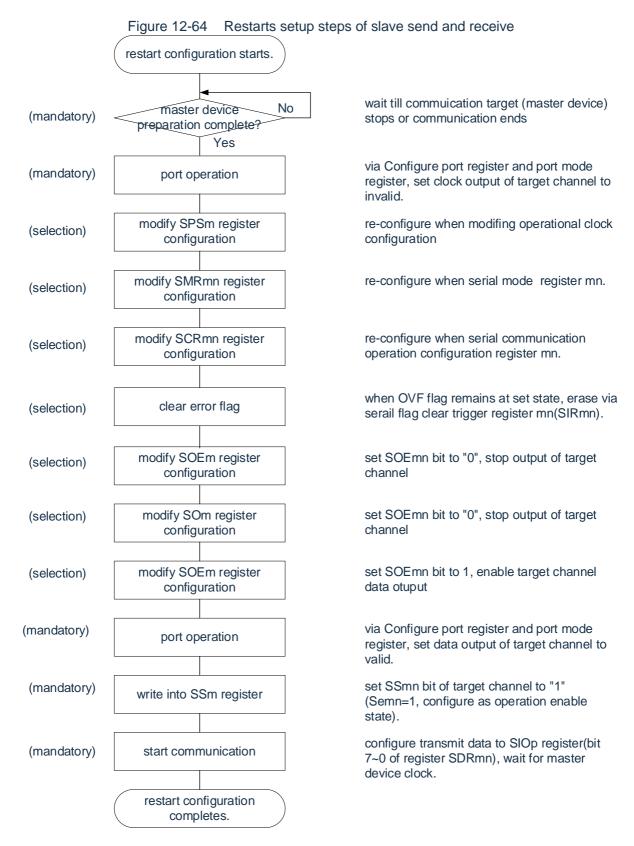

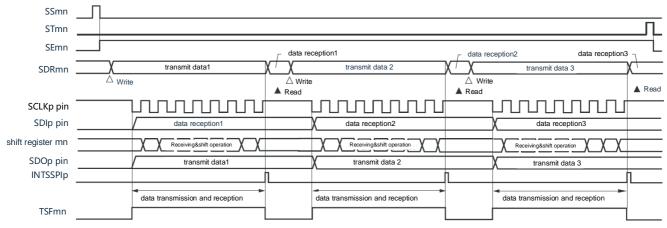

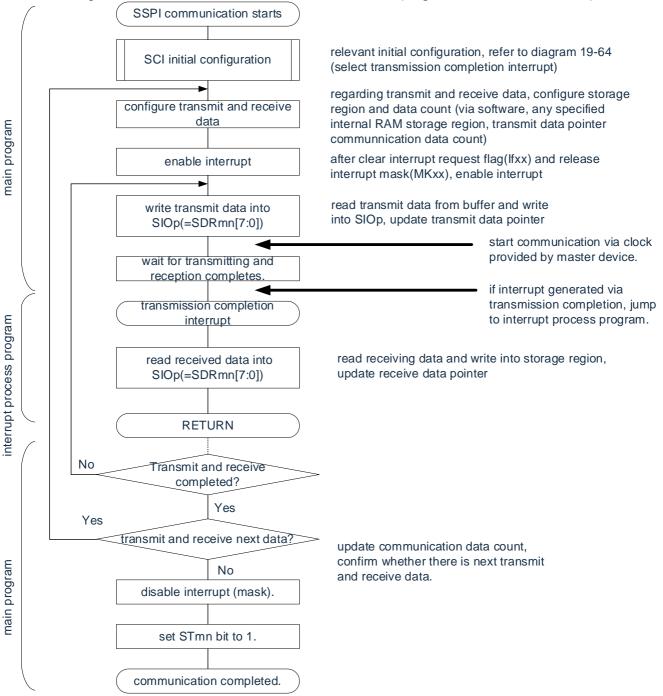

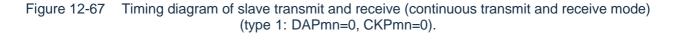

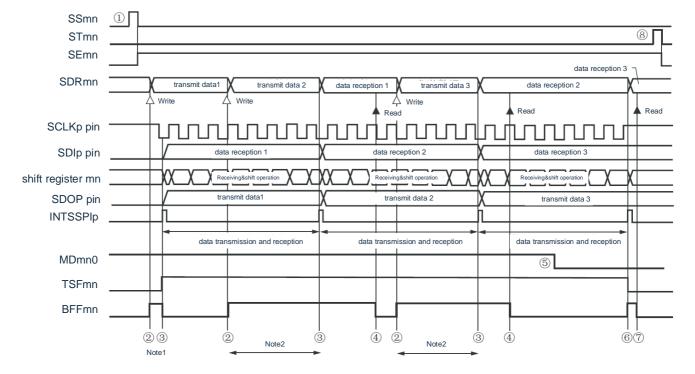

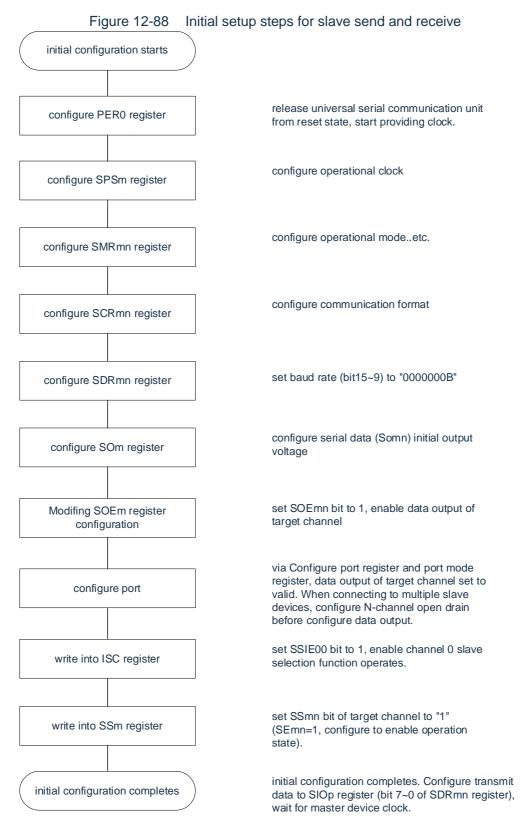

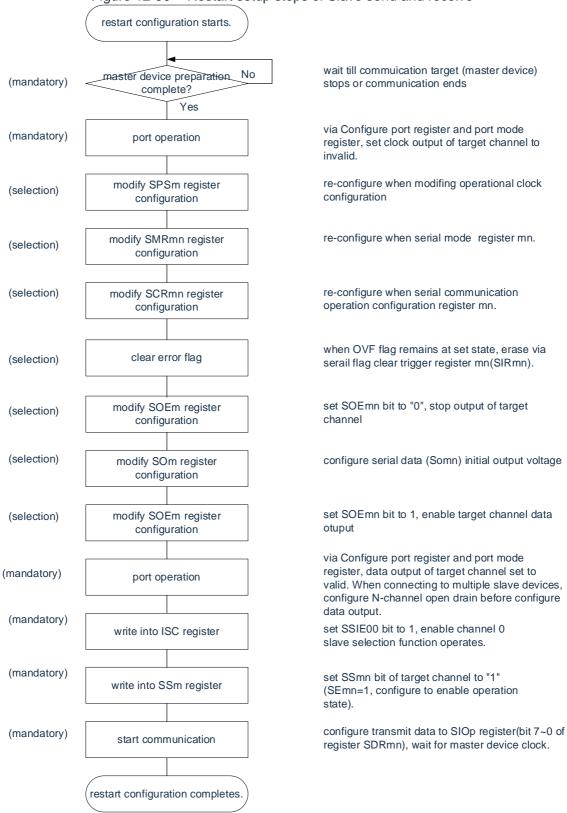

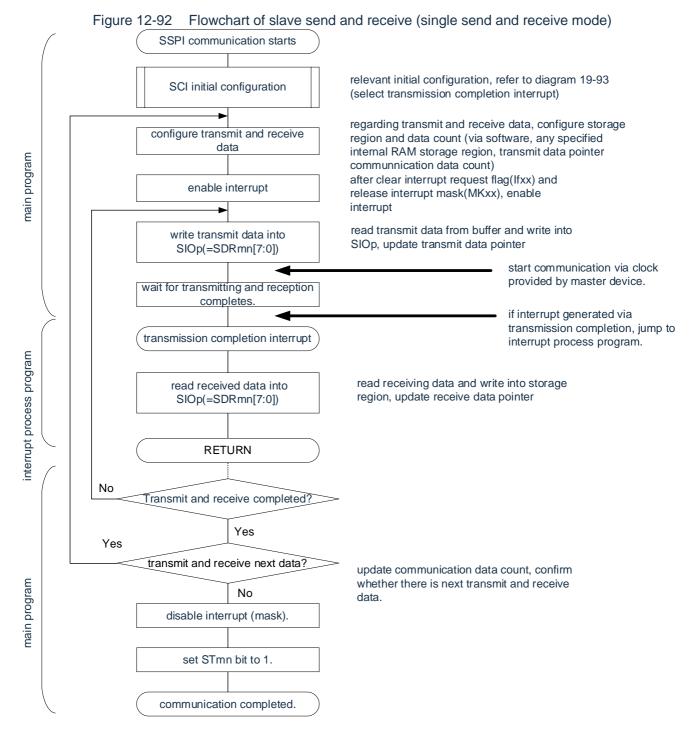

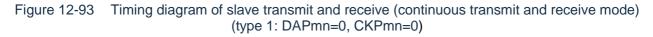

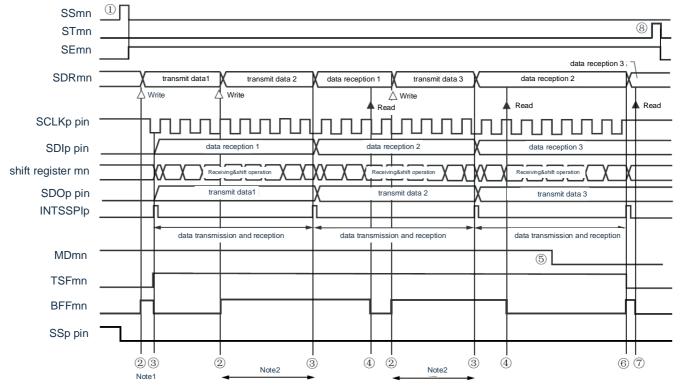

| 12.5.6            | Slave send and receive                                                                               |     |

| 12.5.7            | Calculation of transmit clock frequency                                                              | 377 |

| 12.5.8<br>SSPI11, | Procedure for handling errors during 3-wire serial I/O communication (SSPI00, SSPI07 SSPI20, SSPI21) |     |

| 12.6 Ope          | ration of clock-synchronous serial communication with slave selection input function                 |     |

| 12.6.1            | Slave transmission                                                                                   |     |

| 12.6.2            | Slave receiving                                                                                      |     |

| 12.6.3            | Slave transmission and reception                                                                     | 400 |

| 12.6.4            | Calculation of the transmit clock frequency                                                          | 410 |

| 12.6.5            | Procedure for handling errors during clock-synchronous serial communication with                     |     |

| selectior         | n input function                                                                                     |     |

| 12.7 Ope          | ration of UART (UART0~UART2) communication                                                           | 412 |

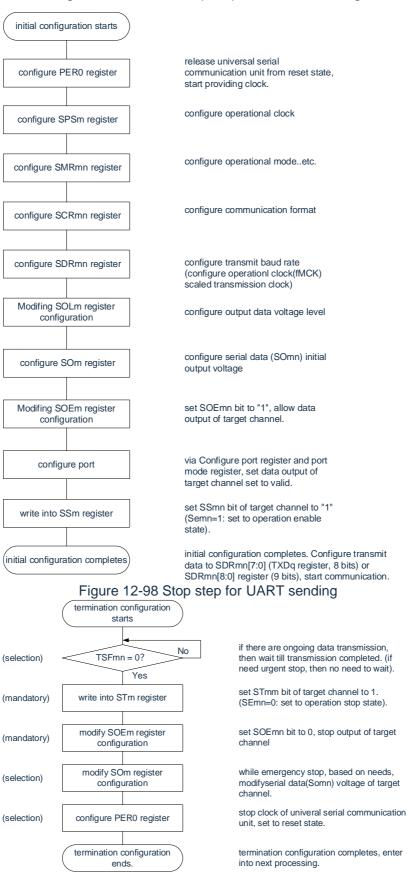

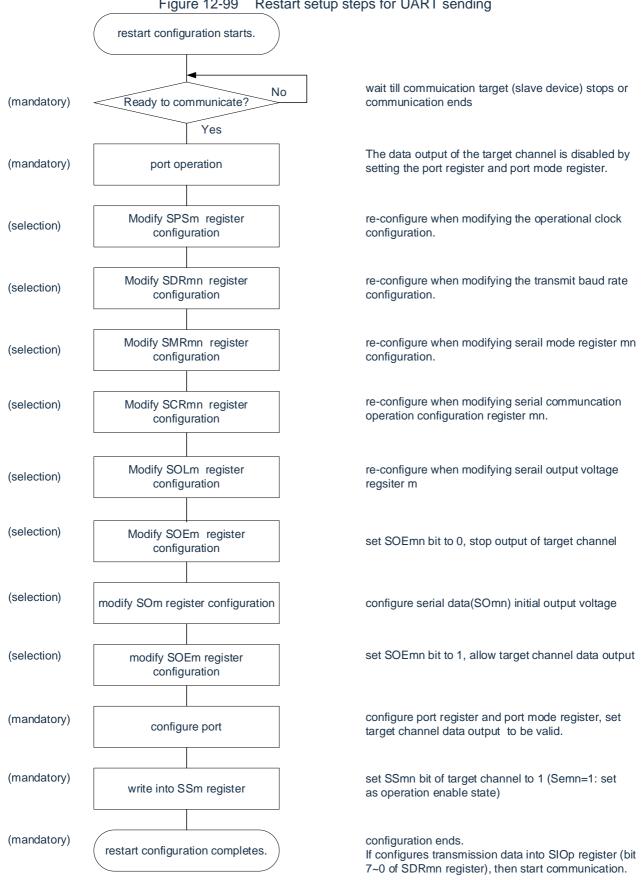

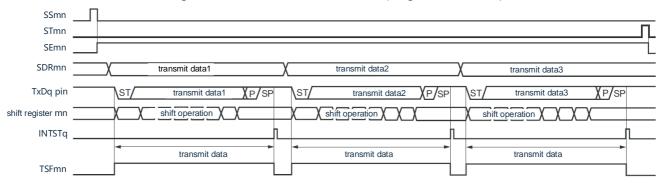

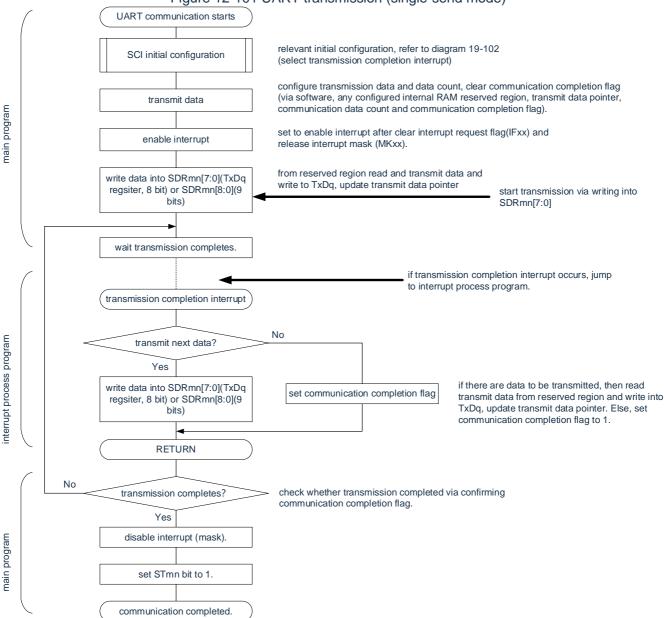

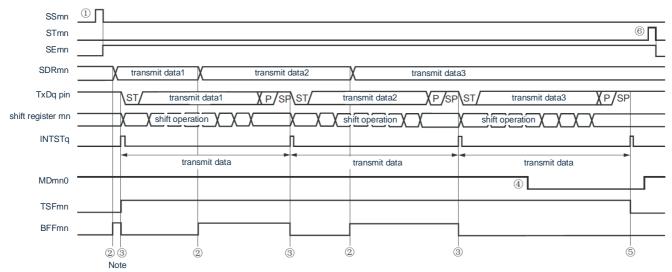

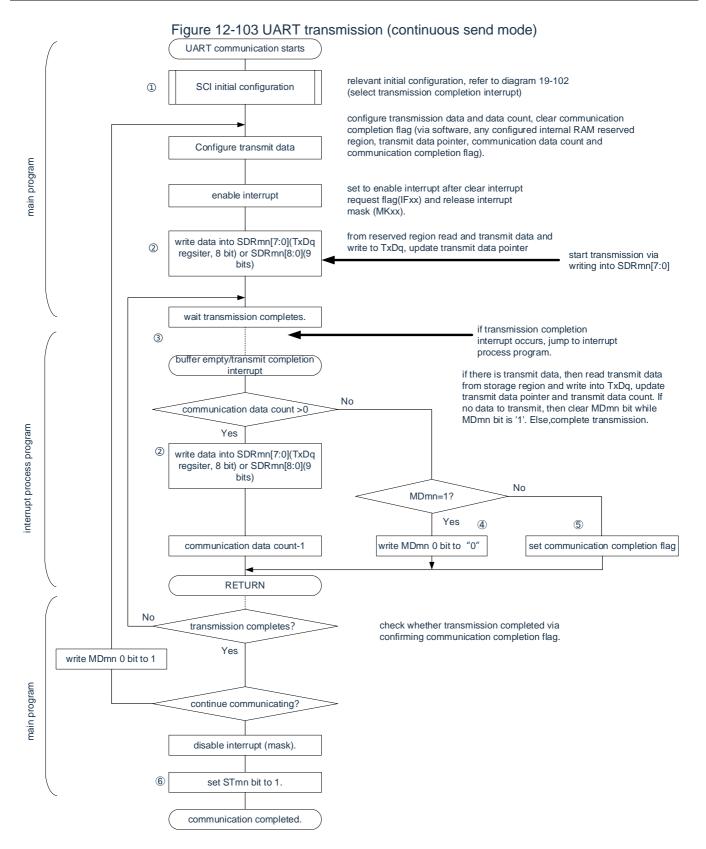

| 12.7.1            | UART transmission                                                                                    | 413 |

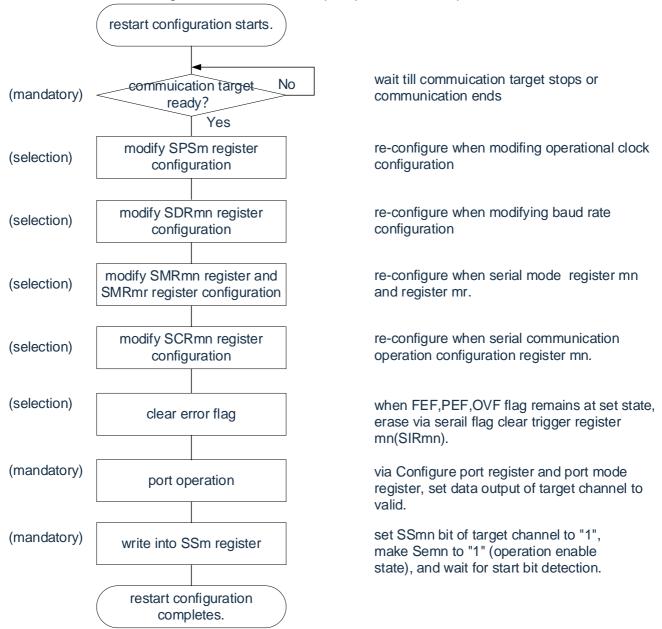

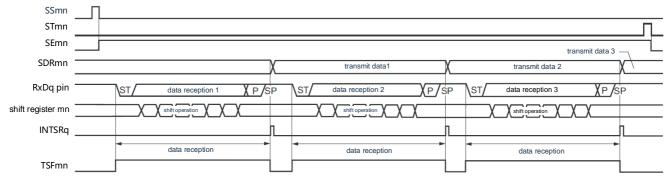

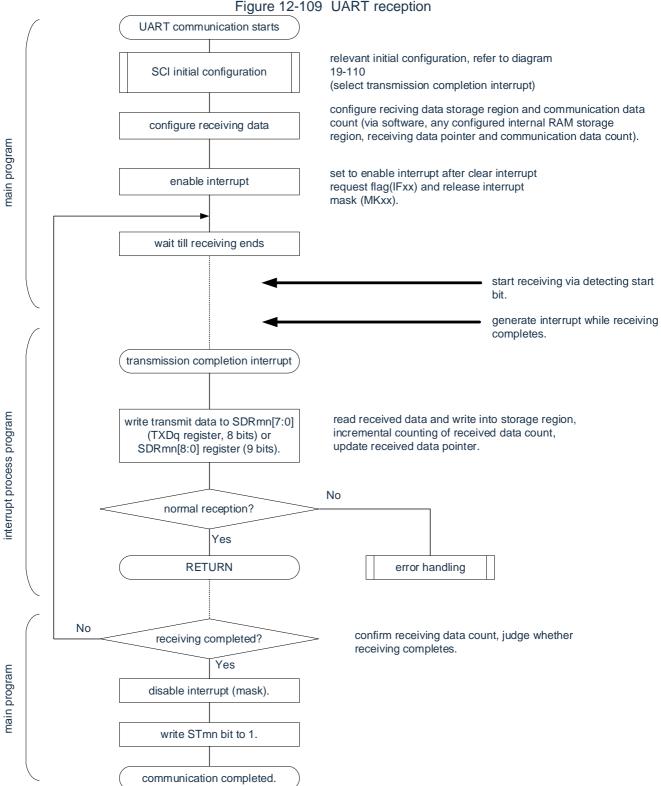

| 12.7.2           | UART reception                                                                                               | 422 |

|------------------|--------------------------------------------------------------------------------------------------------------|-----|

| 12.7.3           | Calculation of the baud rate                                                                                 | 429 |

| 12.7.4           | Handling steps when an error occurs during UART (UART0~UART 2) communication                                 | 433 |

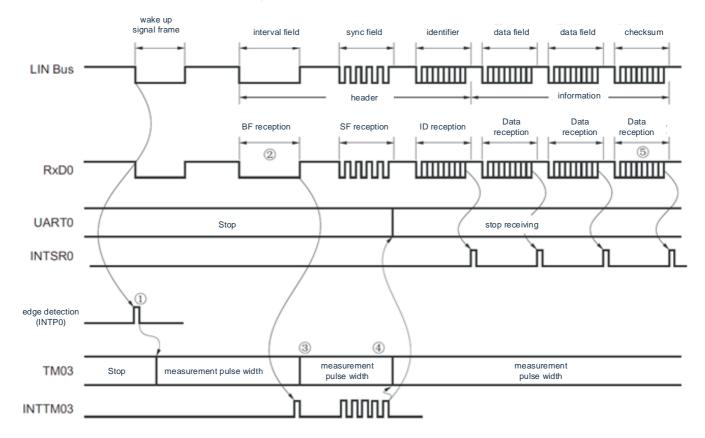

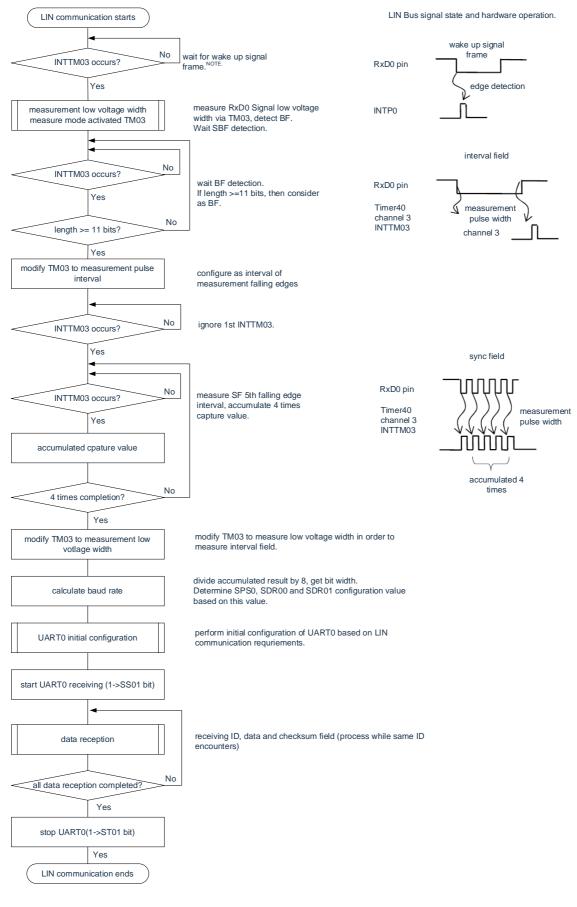

| 12.8 Ope         | ration of LIN communication                                                                                  | 434 |

| 12.8.1           | LIN transmission                                                                                             | 434 |

| 12.8.2           | LIN reception                                                                                                | 437 |

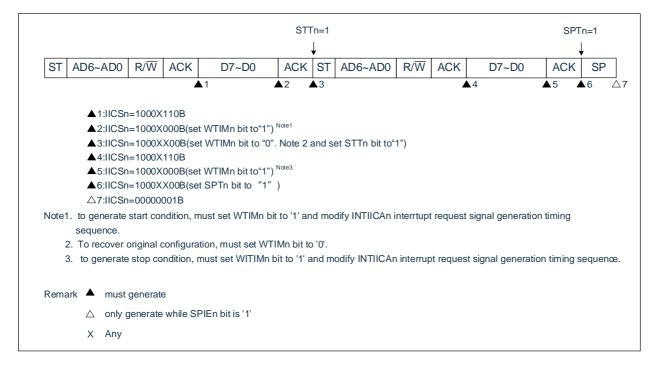

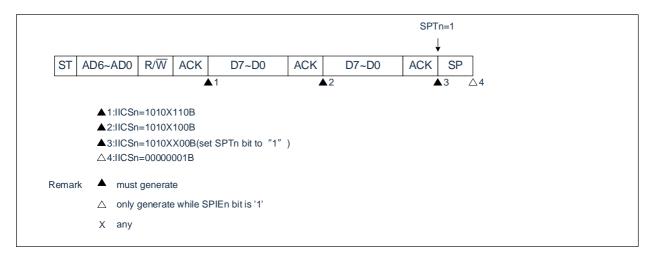

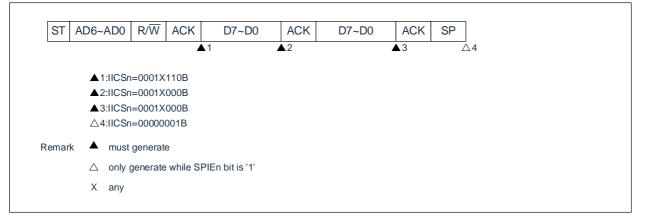

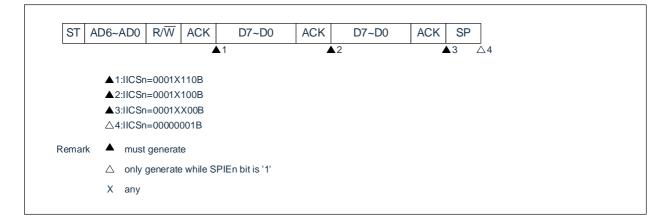

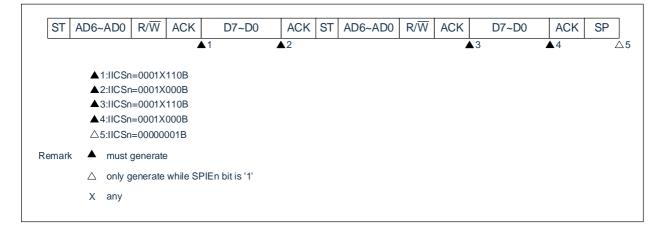

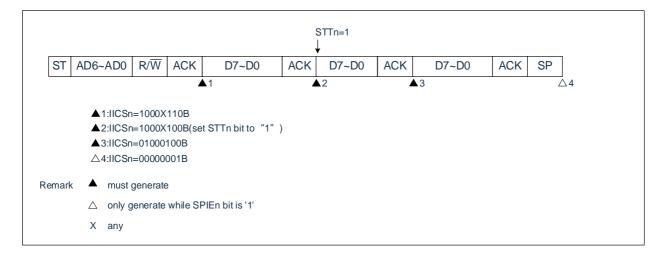

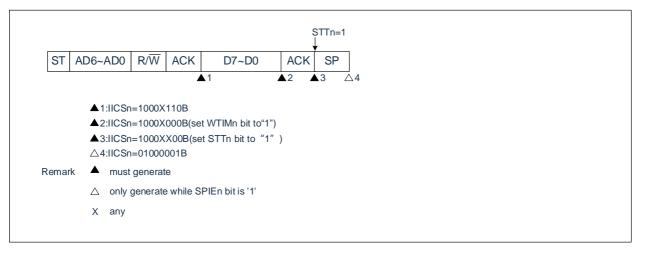

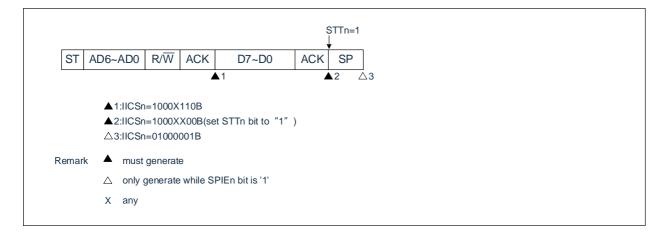

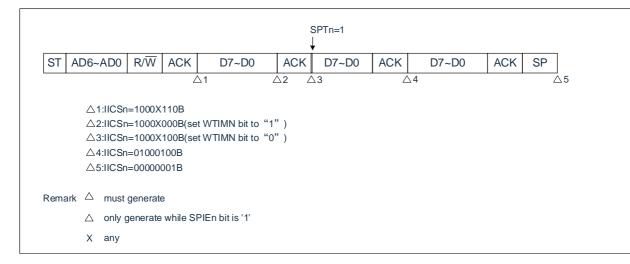

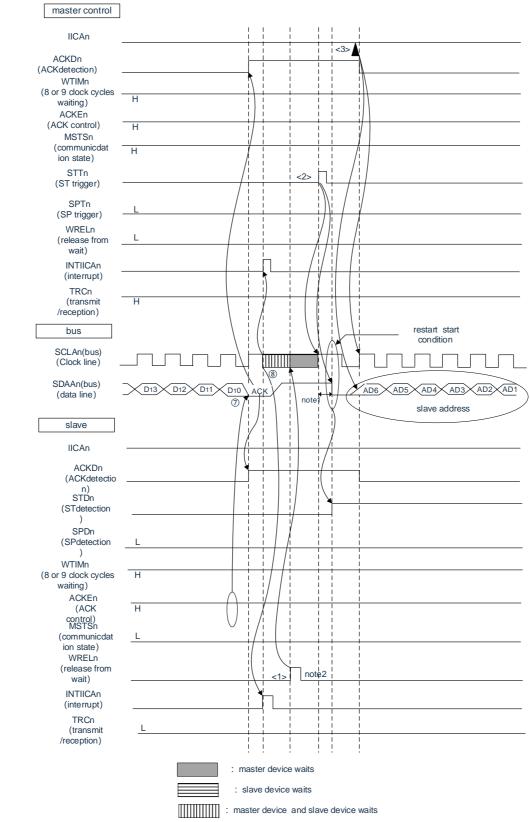

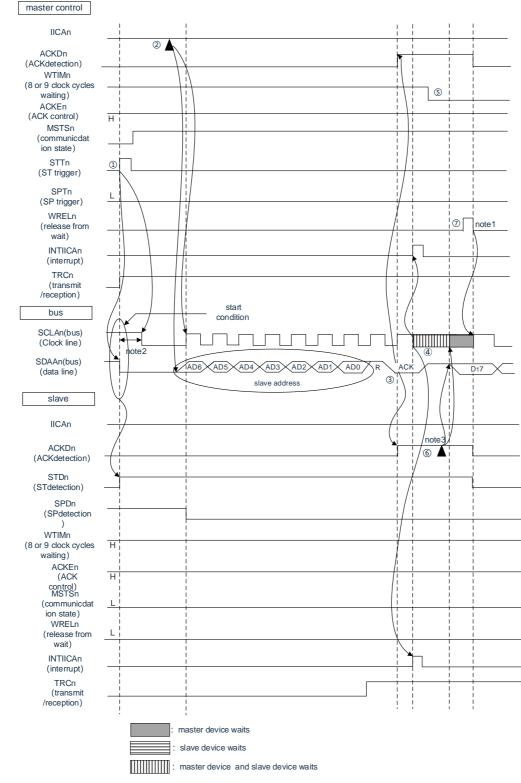

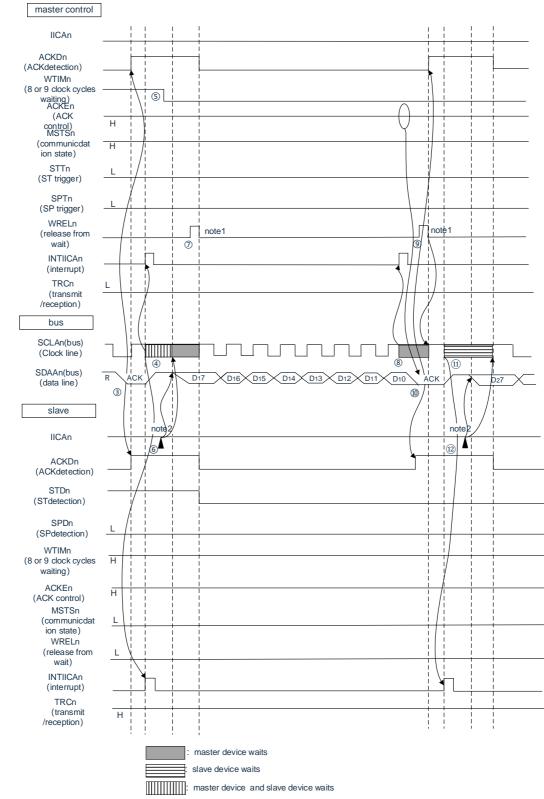

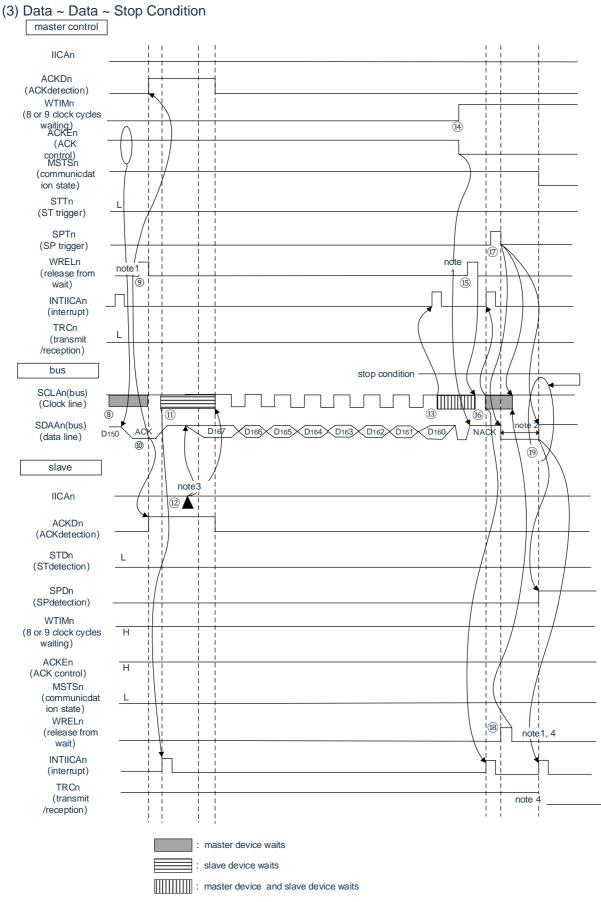

| 12.9 Sim         | plified I <sup>2</sup> C (IIC00, IIC01, IIC10, IIC11, IIC20, IIC21) communication operation                  | 442 |

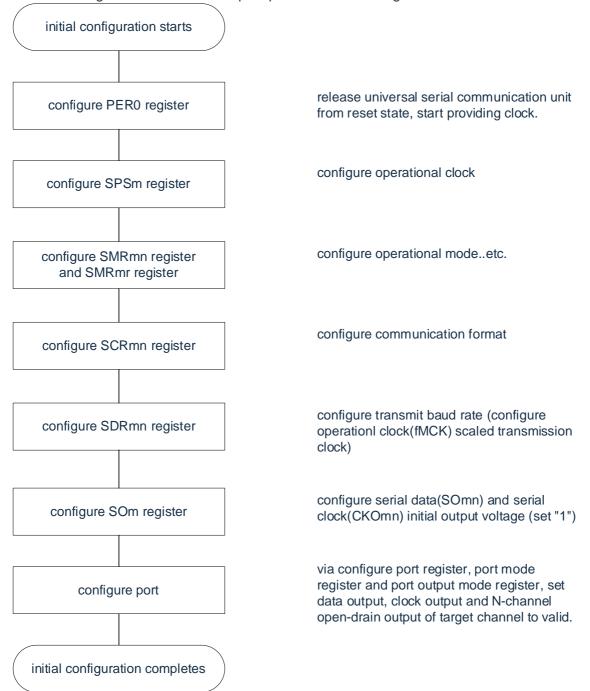

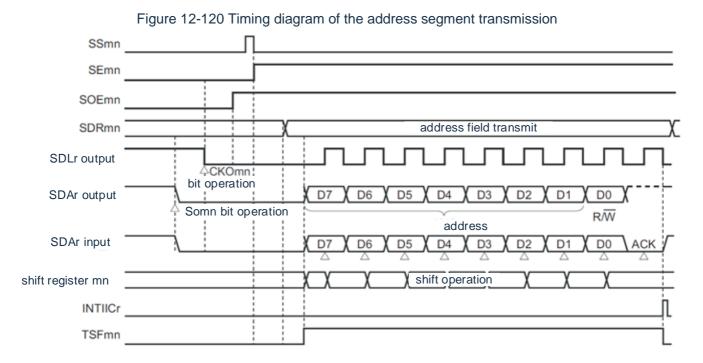

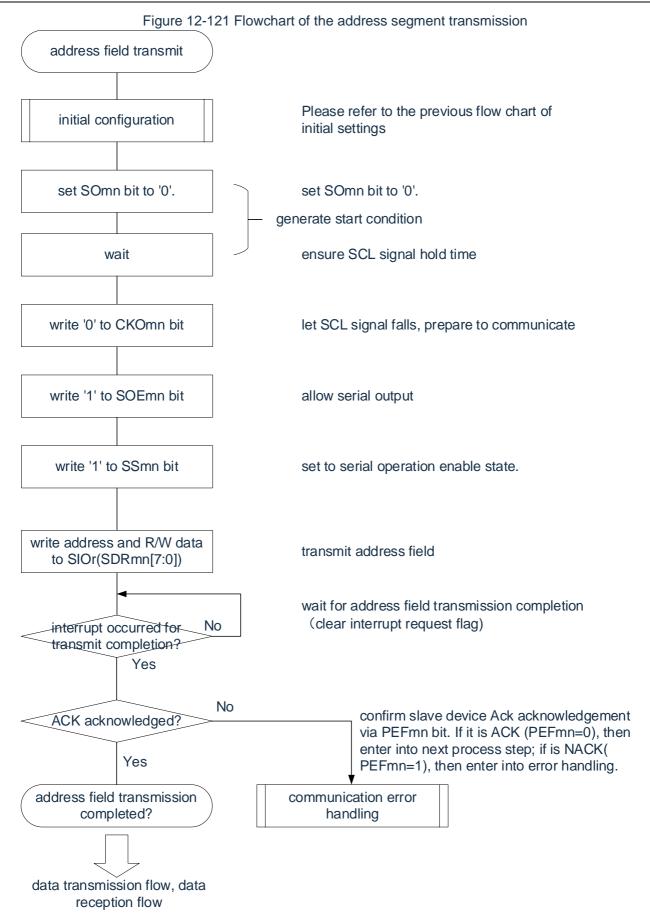

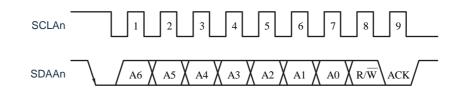

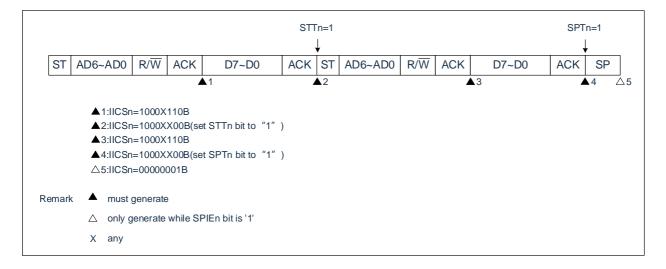

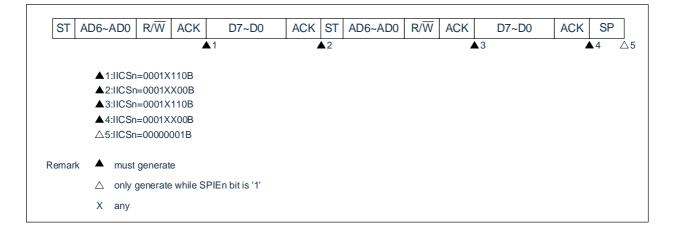

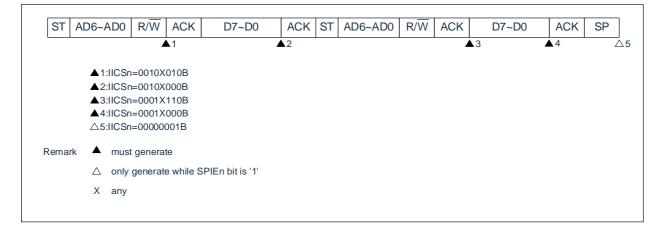

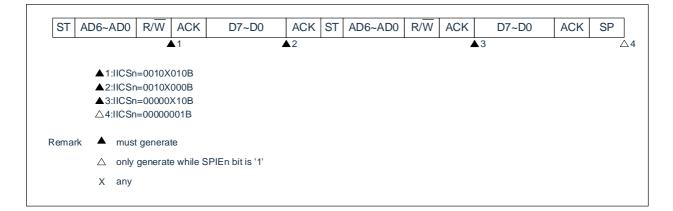

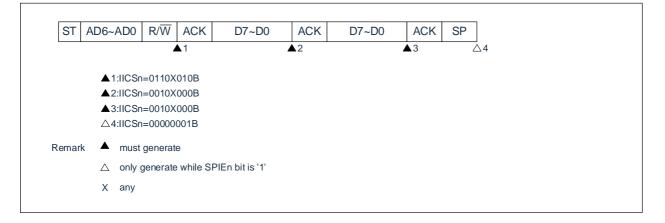

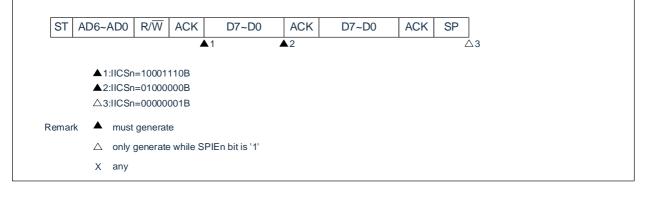

| 12.9.1           | Address segment transmission                                                                                 | 443 |

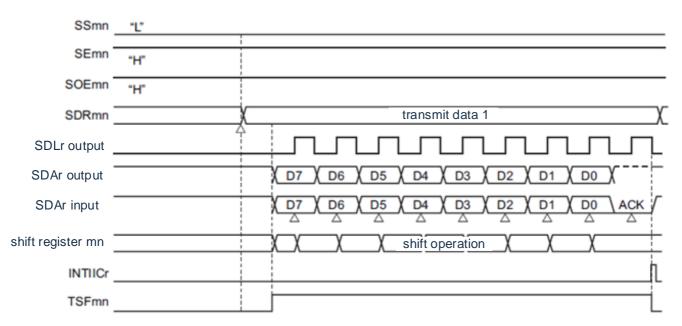

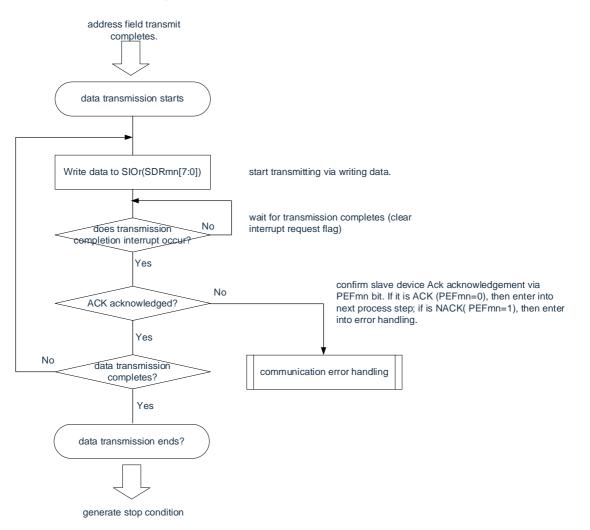

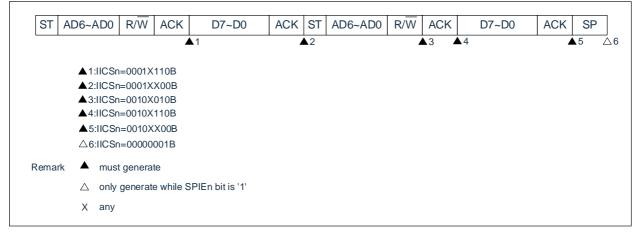

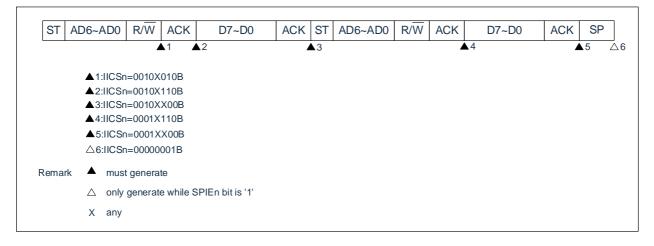

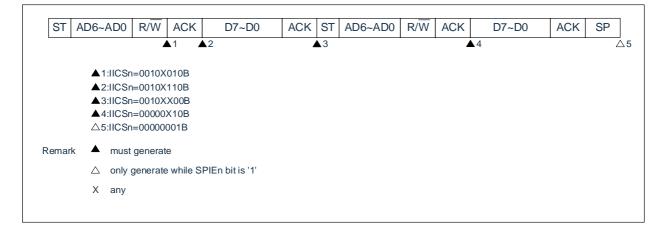

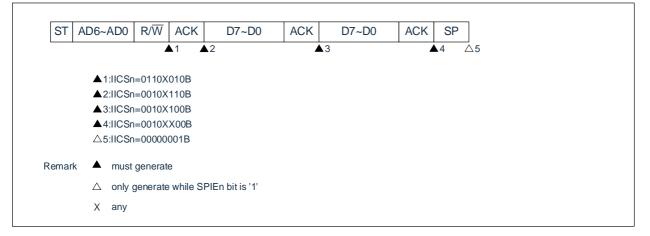

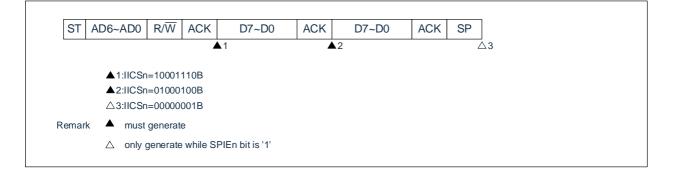

| 12.9.2           | Data transmission                                                                                            | 448 |

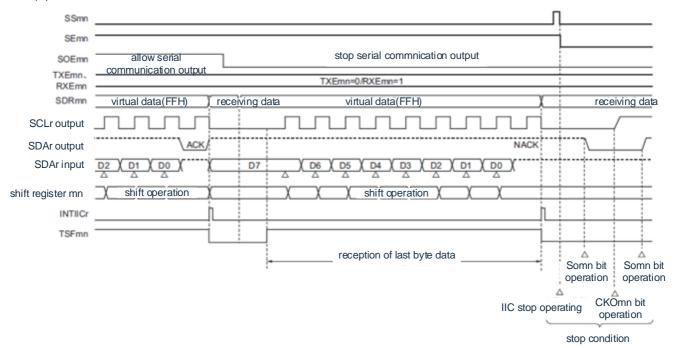

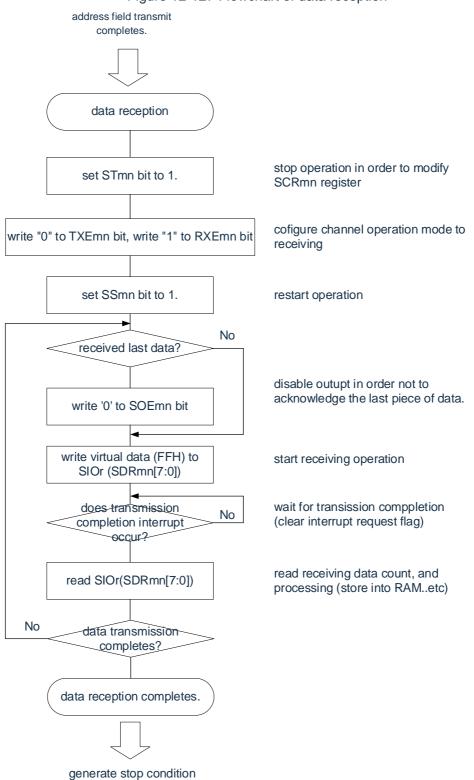

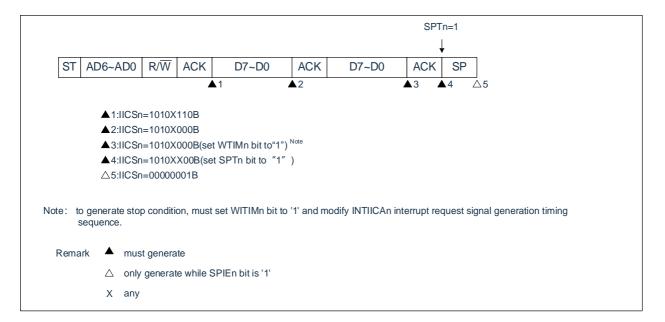

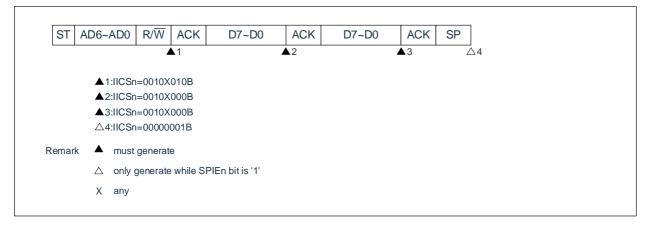

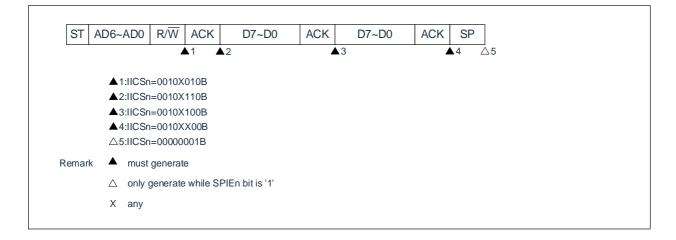

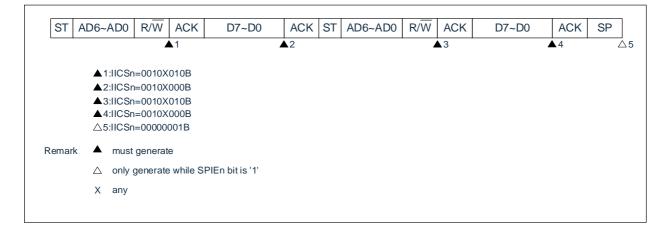

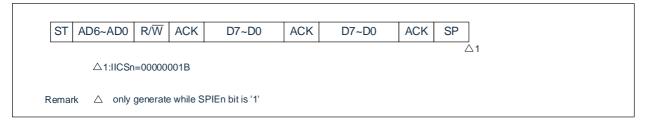

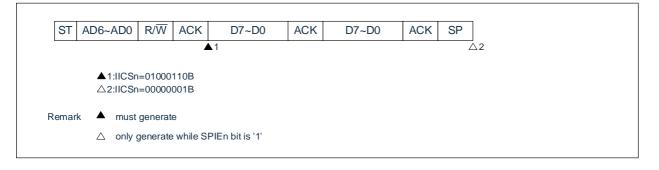

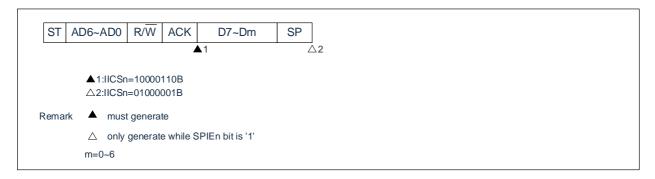

| 12.9.3           | Data reception                                                                                               | 451 |

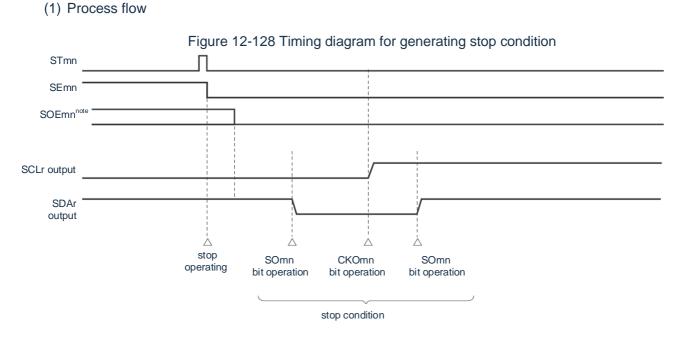

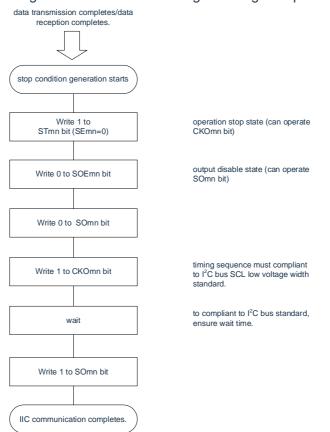

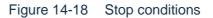

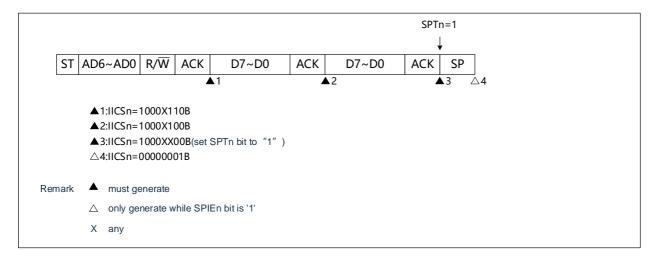

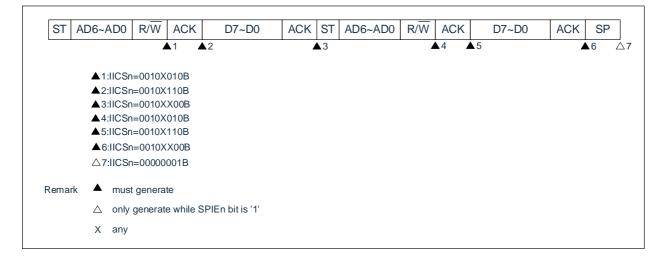

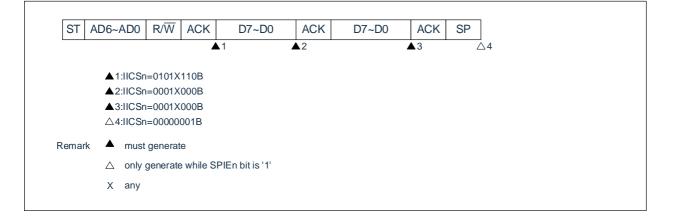

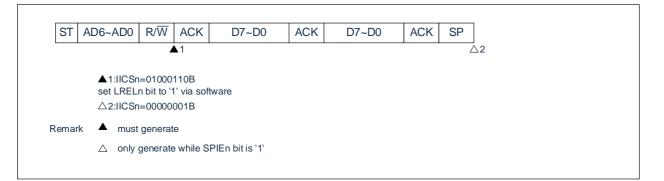

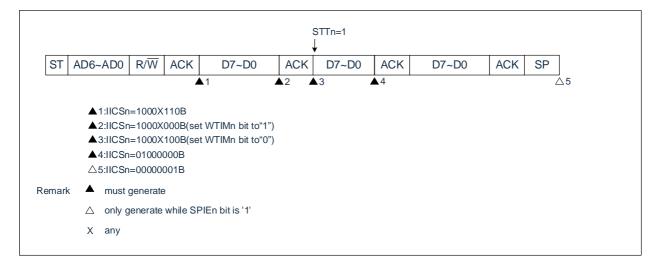

| 12.9.4           | Generation of stop condition                                                                                 | 455 |

| 12.9.5           | Calculation of the transfer rate                                                                             | 456 |

| 12.9.6<br>commur | Processing steps when an error occurs in a simple I2C (IIC00, IIC01, IIC10, IIC11, IIC20<br>nication process |     |

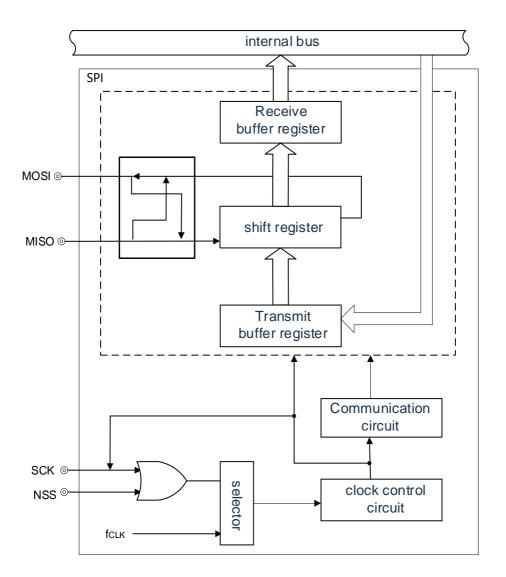

| Chapter 13       | 3 Serial Interface SPI                                                                                       | 459 |

|                  | al interface SPI function                                                                                    | 459 |

|                  | cture of SPI                                                                                                 |     |

|                  | isters for controlling SPI                                                                                   |     |

| 13.3.1           | Peripheral enable register 0 (PER0)                                                                          |     |

| 13.3.2           | SPI operating mode register (SPIM)                                                                           |     |

| 13.3.3           | SPI clock selection register (SPIC)                                                                          |     |

| 13.3.4           | Transmit buffer registers (SDRO)                                                                             |     |

| 13.3.5           | Receive buffer register (SDRI)                                                                               |     |

| 13.3.6           | SPI pin port function control register                                                                       |     |

|                  | eration of SPI                                                                                               |     |

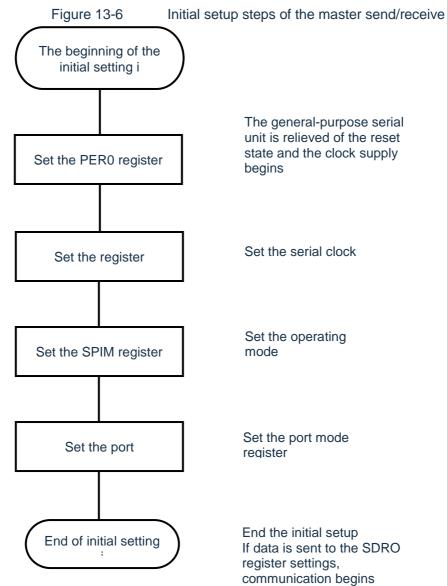

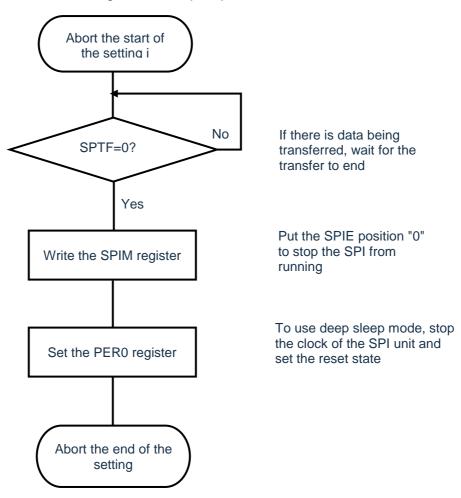

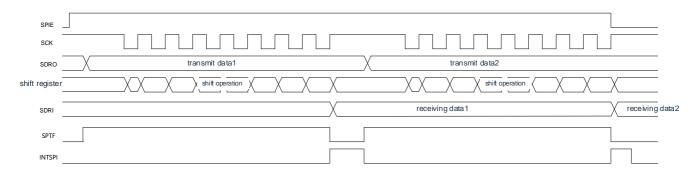

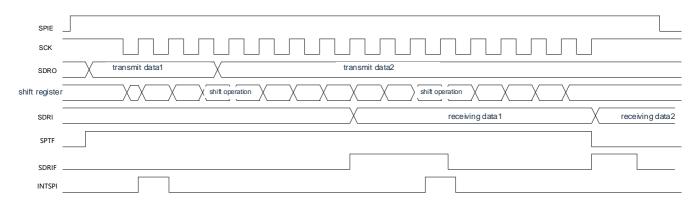

| 13.4.1           | Master tramission and reception                                                                              |     |

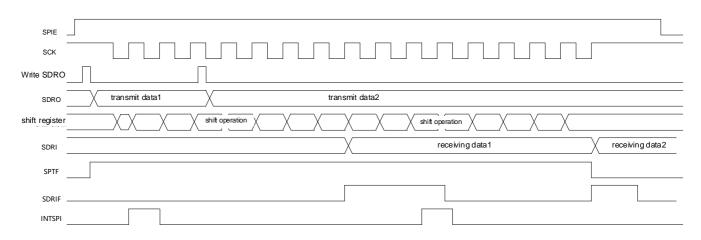

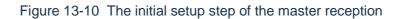

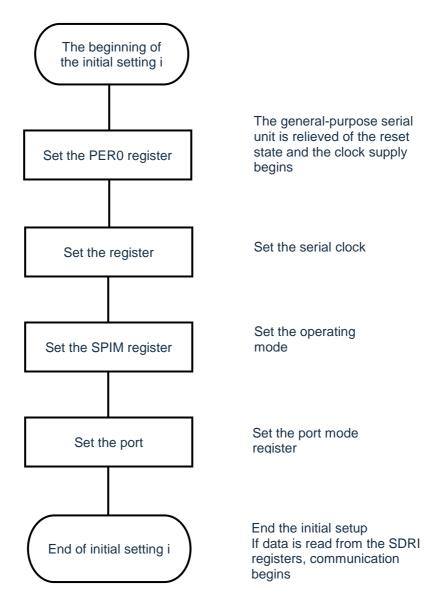

| 13.4.2           | Master reception                                                                                             |     |

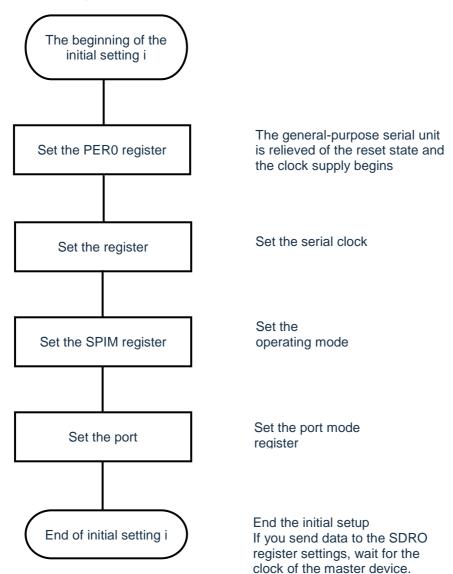

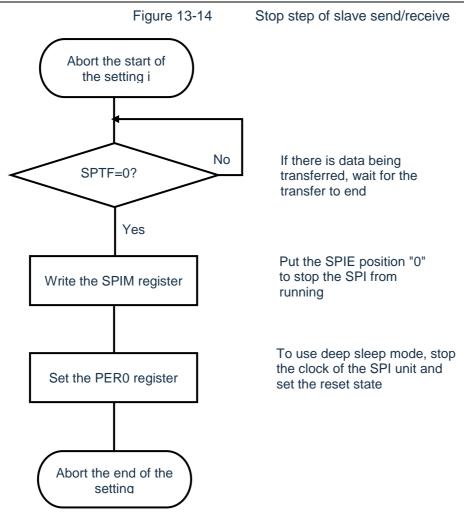

| 13.4.3           | Slave send and receive                                                                                       |     |

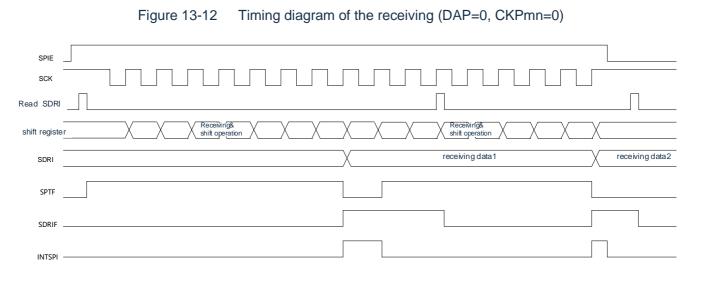

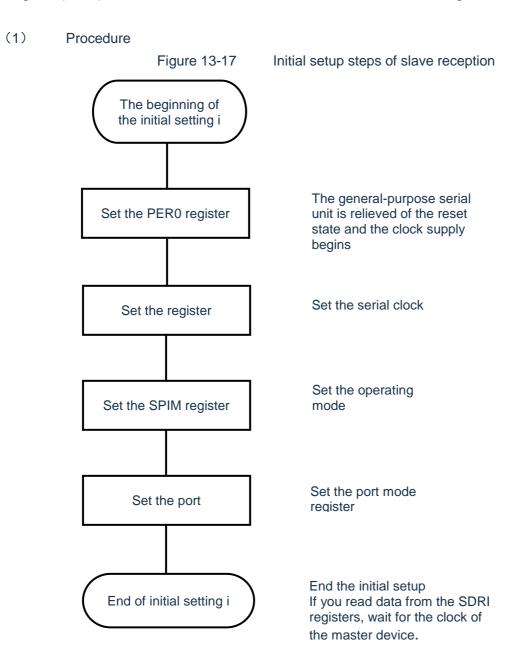

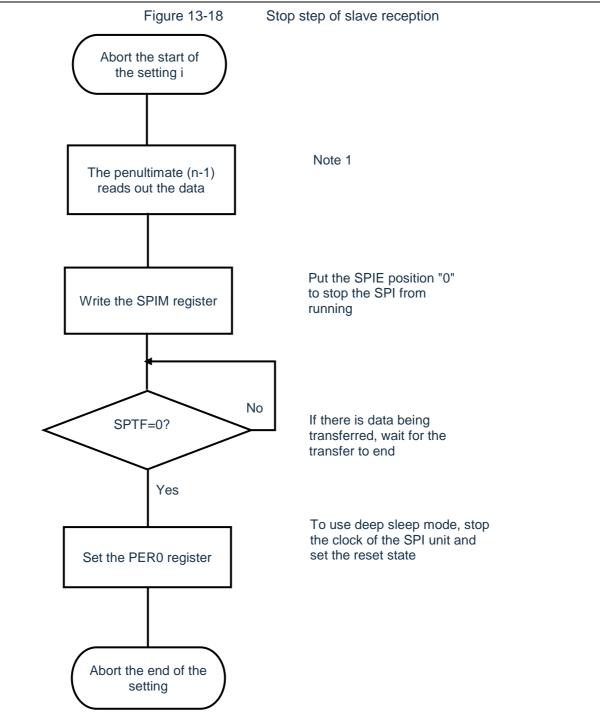

| 13.4.4           | Slave reception                                                                                              |     |

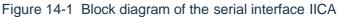

| Chapter 14       |                                                                                                              |     |

| 14.1 Fun         | ction of IICA                                                                                                | 479 |

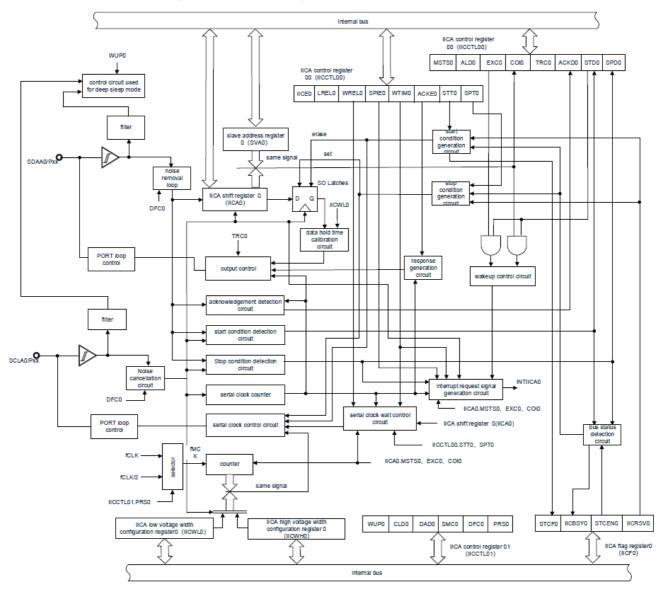

| 14.2 Stru        | cture of the serial interface IICA                                                                           | 482 |

| 14.3 Reg         | isters for controlling serial interface IICA                                                                 | 485 |

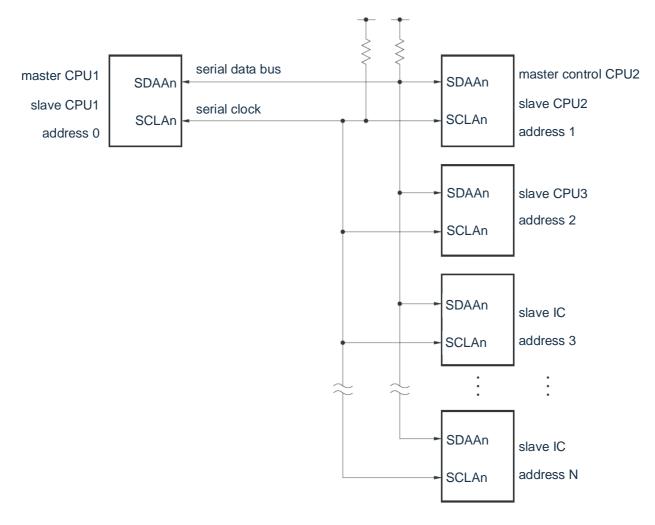

| 14.3.1           | Peripheral enable register 0 (PER0)                                                                          | 486 |

| 14.3.2           | IICA control register n0 (IICCTLn0)                                                                          | 486 |

| 14.3.3           | IICA status register n (IICSn)                                                                               | 491 |

| 14.3.4           | IICA flag register n (IICFn)                                                                                 | 493 |

| 14.3.5           | IICA control register n1 (IICCTLn1)                                                                          | 495 |

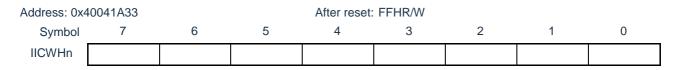

| 14.3.6           | IICA low level width setting register n (IICWLn)                                                             | 497 |

| 14.3.7           | IICA high level width setting register n (IICWHn)                                                            | 497 |

| 14.3.8           | Registers controlling the IICA pin port function                                                             | 498 |

| 14.4 Fun         | ction of I <sup>2</sup> C-bus mode                                                                           | 499 |

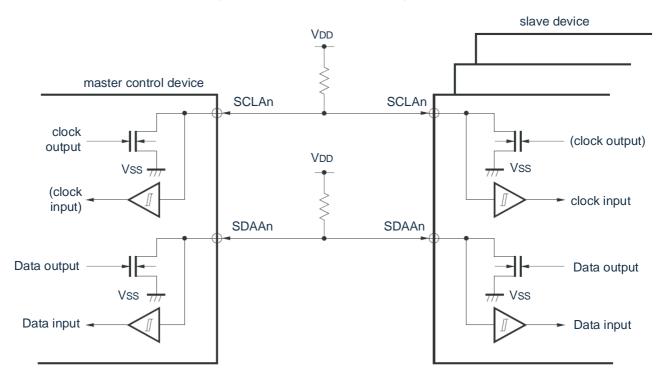

| 14.4.1           | Pin structure                                                                                                | 499 |

| 14.4.2           | Setting the transmit clock via IICWLn register and IICWHn register                                           |     |

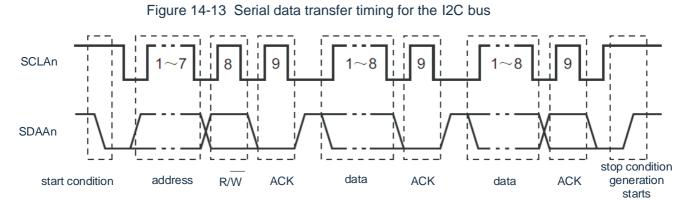

| 14.5 Defi        | nition and control method of I <sup>2</sup> C-bus                                                            | 501 |

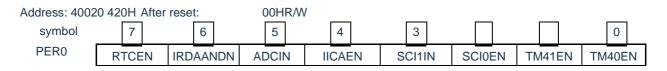

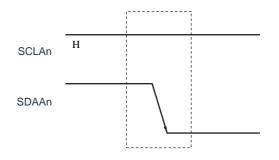

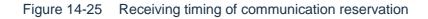

| 14.5.1           | Start conditions                                                                                             | 502 |

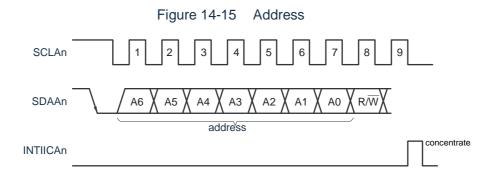

| 14.5.2           | Address                                                                                                      | 503 |

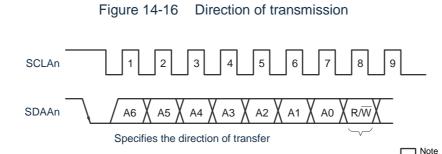

| 14.5.3     | Designation of transmission direction                              | 503 |

|------------|--------------------------------------------------------------------|-----|

| 14.5.4     | Acknowledge (ACK)                                                  | 504 |

| 14.5.5     | Stop Conditions                                                    | 505 |

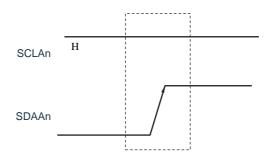

| 14.5.6     | Wait                                                               | 506 |

| 14.5.7     | Release method of wait                                             | 508 |

| 14.5.8     | Interrupt request (INTIICAn) generation timing and wait control    | 509 |

| 14.5.9     | Detection method for address matching                              |     |

| 14.5.10    | Detection of errors                                                | 510 |

| 14.5.11    | Extension code                                                     | 511 |

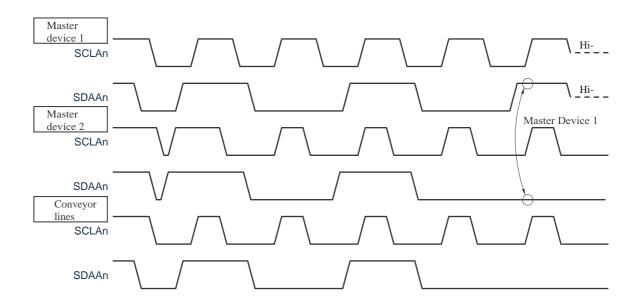

| 14.5.12    | Arbitration                                                        | 512 |

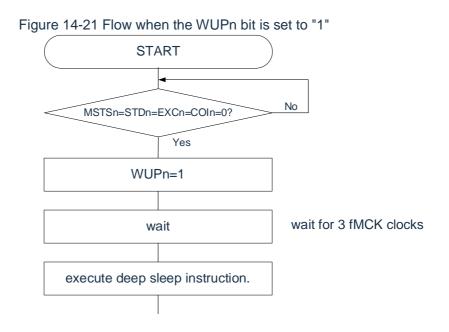

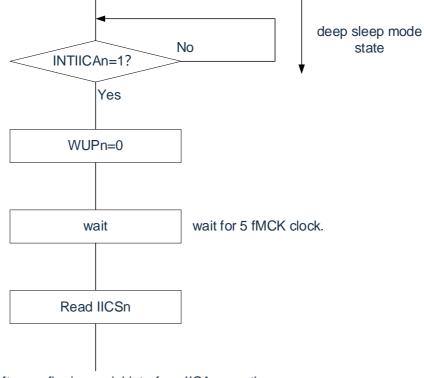

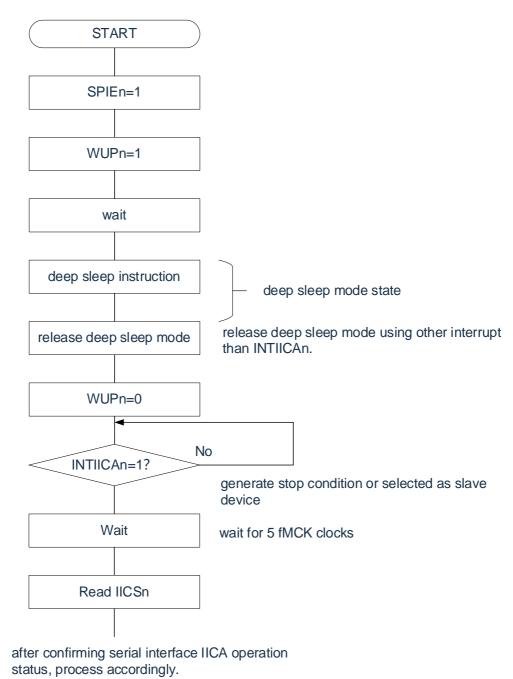

| 14.5.13    | Wake-up function                                                   | 514 |

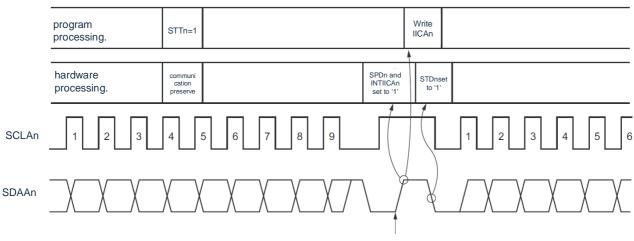

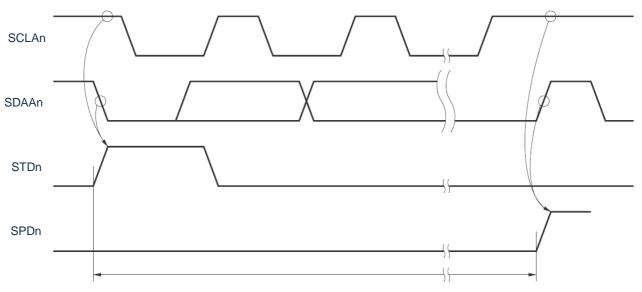

| 14.5.14    | Communicate with reservation                                       | 517 |

| 14.5.15    | Other cautions                                                     |     |

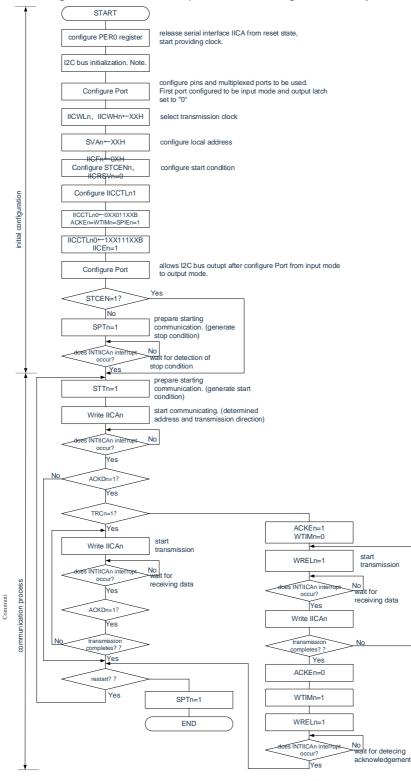

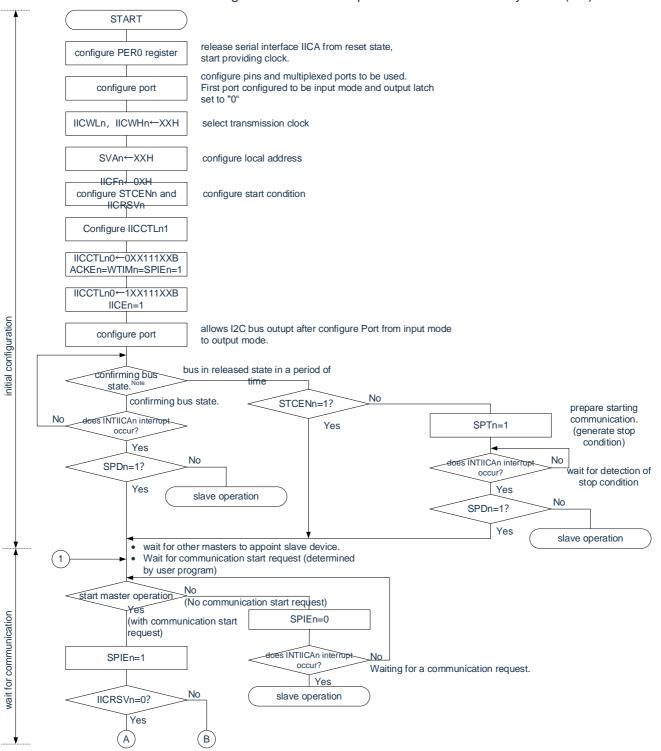

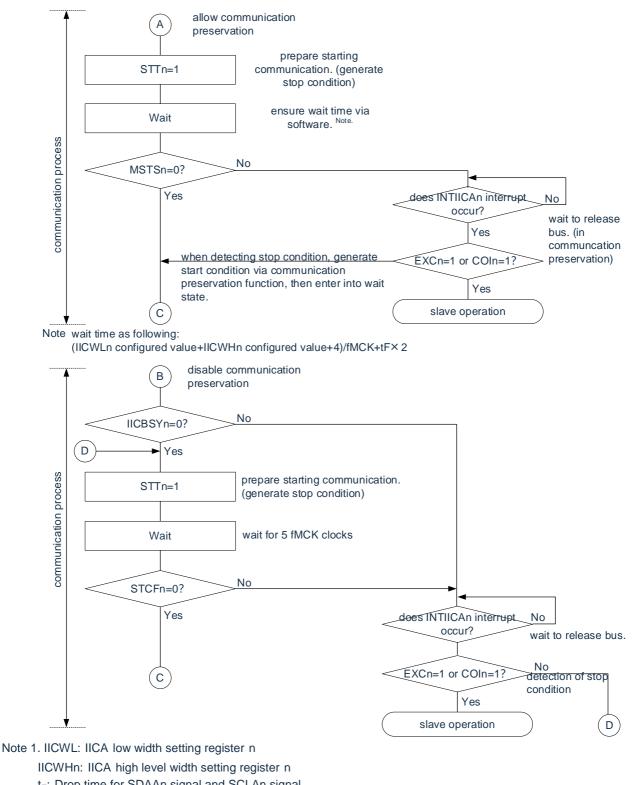

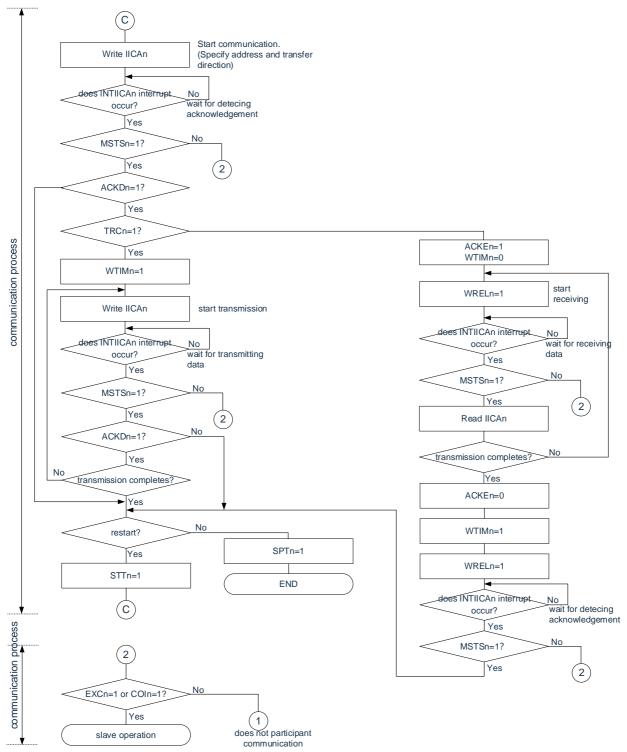

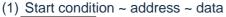

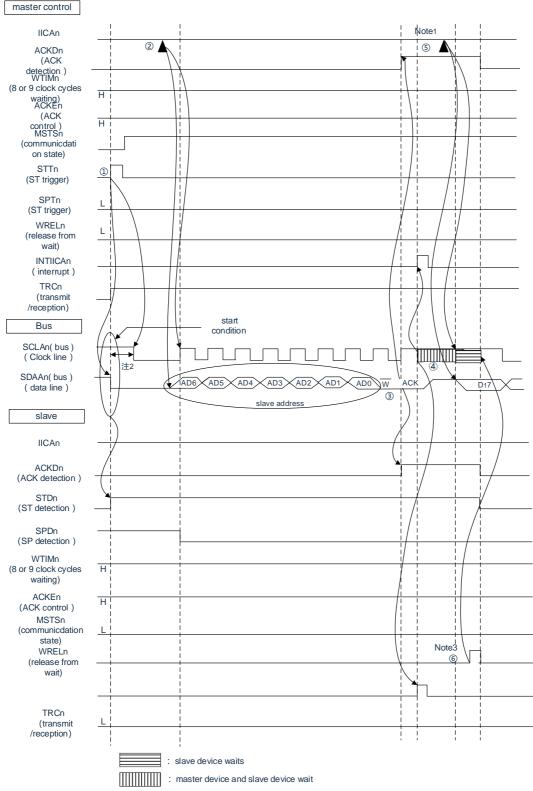

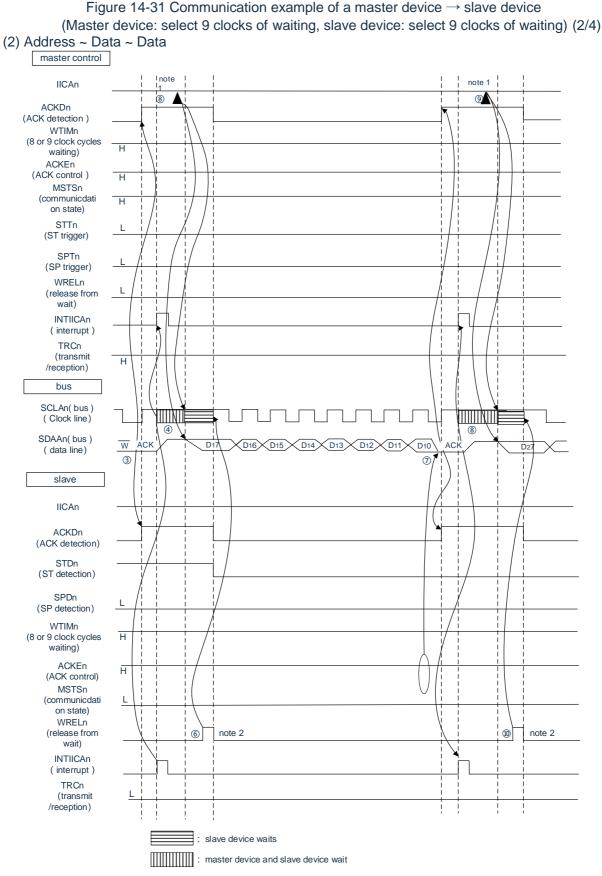

| 14.5.16    | Communication operation                                            |     |

| 14.5.17    | Generation timing of I <sup>2</sup> C interrupt request (INTIICAn) | 531 |

|            | ng diagram                                                         |     |

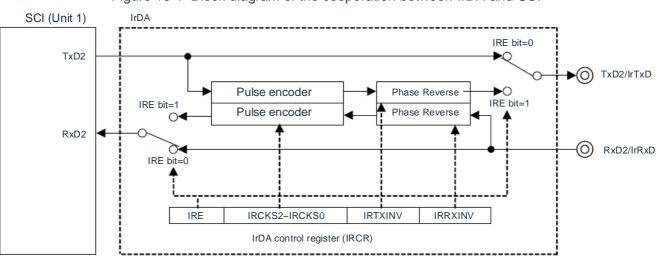

| Chapter 15 | 5 IrDA                                                             | 568 |

|            |                                                                    |     |

|            | ction of IrDA                                                      |     |

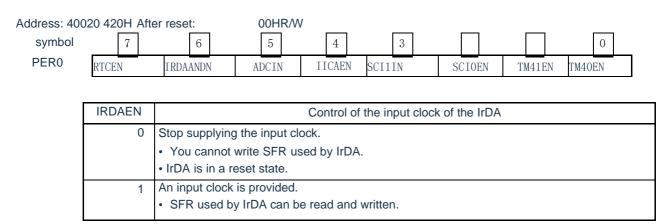

| 0          | sters for controlling the IrDA                                     |     |

| 15.2.1     | Peripheral enable register 0 (PER0)                                |     |

| 15.2.2     | IrDA control register (IRCR)                                       |     |

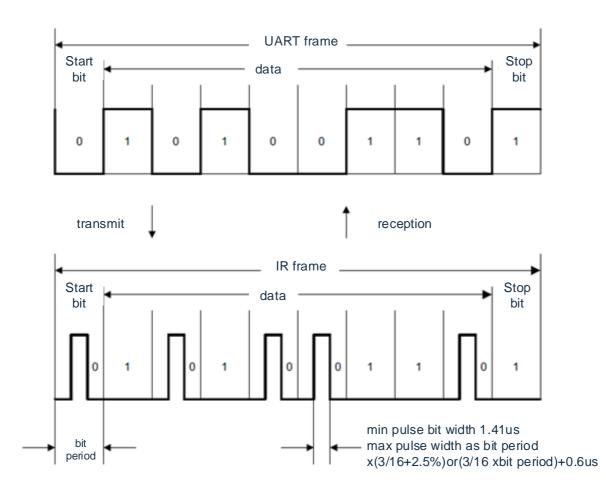

|            | ration of IrDA                                                     |     |

| 15.3.1     | Operating steps for IrDA communication                             |     |

| 15.3.2     | Transmission                                                       |     |

| 15.3.3     | Reception                                                          |     |

| 15.3.4     | High level pulse width selection                                   |     |

| 15.4 Con   | siderations when using IrDA                                        | 573 |

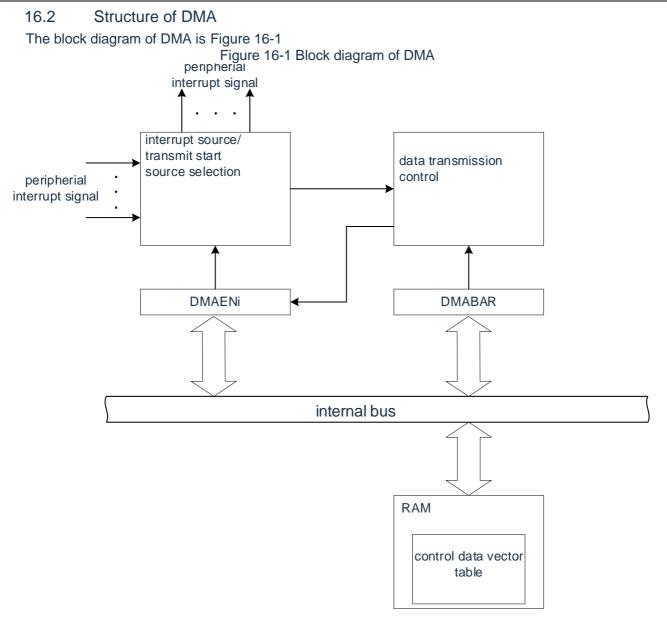

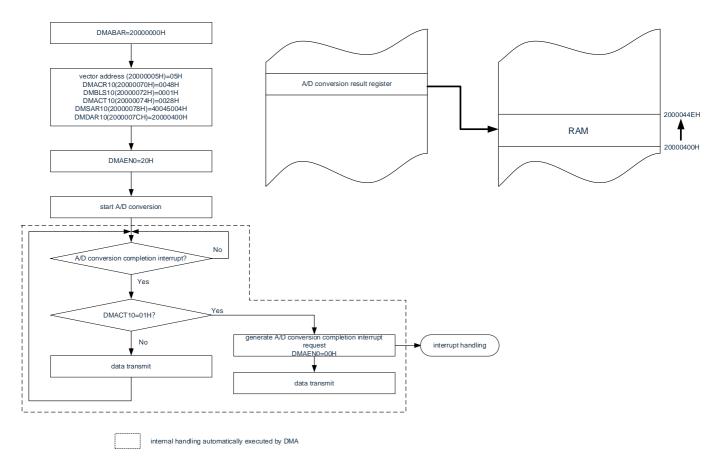

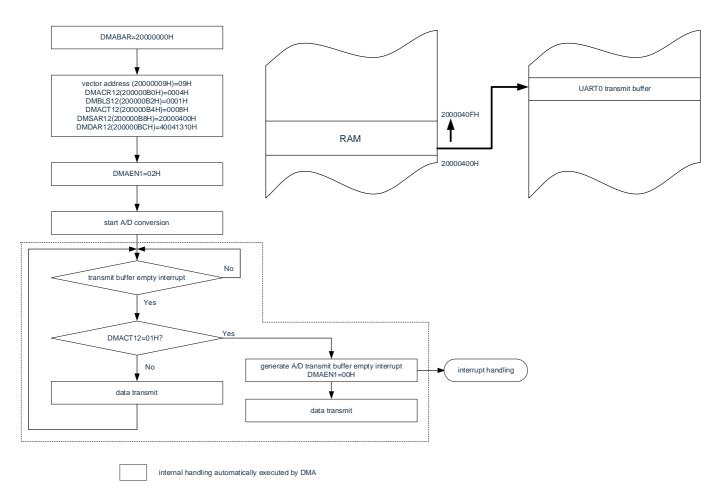

| Chapter 16 | Enhanced DMA                                                       | 574 |

| 16.1 The   | function of DMA                                                    | 574 |

| 16.2 Strue | cture of DMA                                                       |     |

| 16.3 Regi  | sters for controlling DMA                                          | 577 |

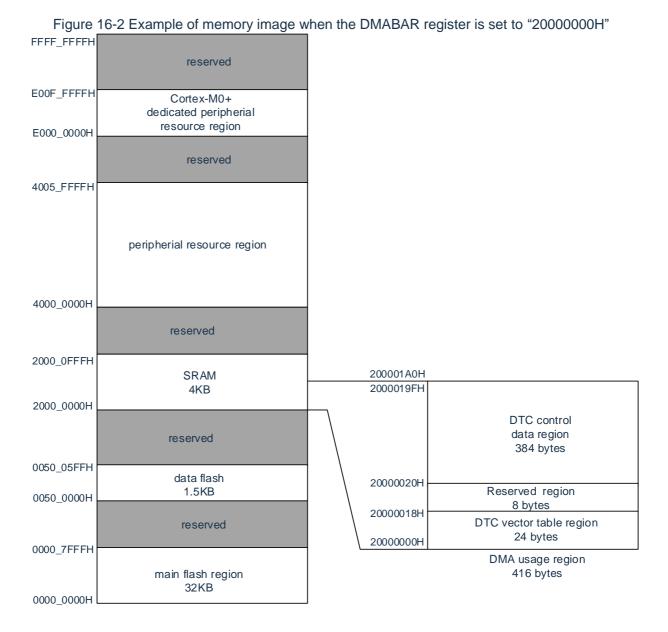

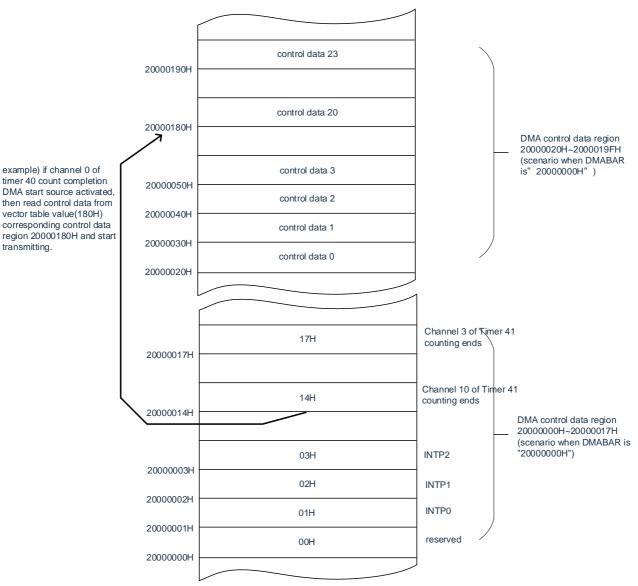

| 16.3.1     | DMA control data areas and DMA vector table areas allocation       |     |

| 16.3.2     | Control data allocation                                            |     |

| 16.3.3     | Vector table                                                       |     |

| 16.3.4     | Peripheral Enable Register 1 (PER1)                                |     |

| 16.3.5     | DMA control register j(DMACRj) (j=0~23).                           |     |

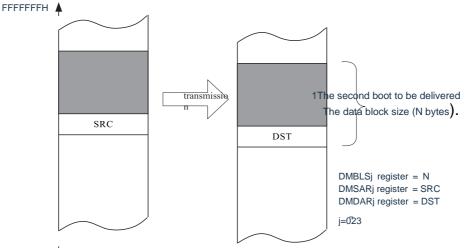

| 16.3.6     | DMA block size register j (DMBLSj) (j=0~23)                        |     |

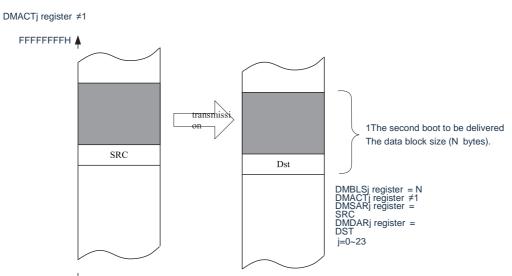

| 16.3.7     | DMA transmit count register j(DMACTj) (j=0~23)                     |     |

| 16.3.8     | DMA transmit count reload register j(DMRLDj) (j=0~23)              |     |

| 16.3.9     | DMA source address register j(DMSARj) (j=0~23).                    |     |

|            | DMA destination address register j(DMDARj) (j=0~23)                |     |

|            | DMA boot enable register i (DMAENi) ( $i=0~2$ ).                   |     |

|            | DMA base address register (DMABAR).                                |     |

|            | operation                                                          |     |

| 16.4.1     | Start the source                                                   |     |

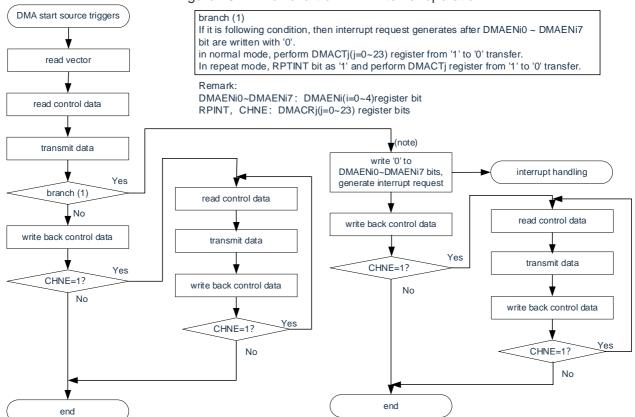

| 16.4.2     | Normal mode                                                        |     |

| 10.1.2     |                                                                    |     |

| 16.4.3           | Repeat pattern                                                                         |     |

|------------------|----------------------------------------------------------------------------------------|-----|

| 16.4.4           | Chain transfer                                                                         |     |

|                  | autions when using DMA                                                                 |     |

| 16.5.1           | DMA controls the settings of data and vector tables                                    |     |

| 16.5.2           | DMA controls the allocation of data areas and DMA vector table areas                   |     |

| 16.5.3<br>16.5.4 | Number of execution clocks for DMA                                                     |     |

| 16.5.4           | Response time of DMA<br>Startup source for DMA                                         |     |

| 16.5.6           | Operation in standby mode                                                              |     |

| Chapter 17       |                                                                                        |     |

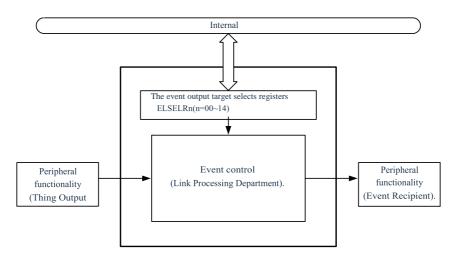

|                  | ure of EVENTC                                                                          |     |

|                  | cture of EVENTC                                                                        |     |

|                  | trol registers                                                                         |     |

| 17.3.1           | Output target selection register n (ELSELRn) (n=00~14)                                 |     |

| 17.4 Ope         | ration of EVENTC                                                                       |     |

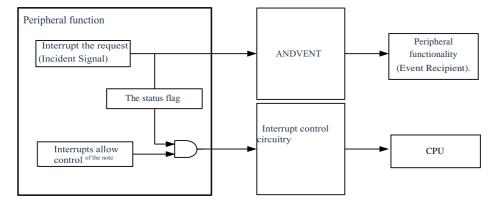

| Chapter 18       | 3 Interrupt Function                                                                   | 611 |

|                  | es of interrupt function                                                               |     |

|                  | rupt source and structure                                                              |     |

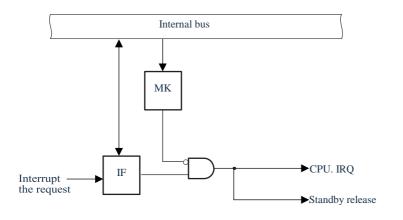

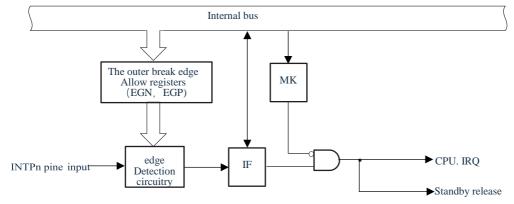

|                  | isters controlling interrupt function                                                  |     |

| 18.3.1           | Interrupt request flag registers (IF00 to IF31)                                        |     |

| 18.3.2           | Interrupt mask flag register (MK00~MK31)                                               |     |

| 18.3.3           | External interrupt rising edge enable register (EGP0), External interrupt falling edge |     |

|                  | (EGN0)                                                                                 | -   |

| 18.4 Ope         | ration of interrupt handling                                                           |     |

| 18.4.1           | Acceptance of maskable interrupt requests                                              | 622 |

| 18.4.2           | Acceptance of non-maskable interrupt requests                                          | 622 |

| Chapter 19       | 9 Key Interrupt Function                                                               | 623 |

|                  | ction of key interrupt                                                                 |     |

| 19.2 Stru        | cture of key interrupt                                                                 | 623 |

| 0                | isters for controlling key interrupt                                                   |     |

| 19.3.1           | Key return mode register (KRM)                                                         |     |

| 19.3.2           | Port mode register (PMx)                                                               | 626 |

| Chapter 20       | ) Standby Function                                                                     | 627 |

| 20.1 Star        | dby function                                                                           | 627 |

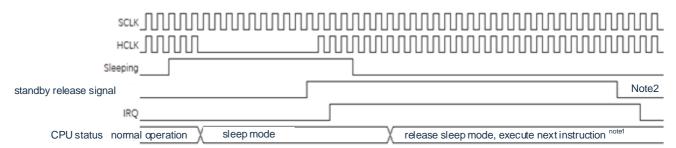

| 20.2 Slee        | p mode                                                                                 | 628 |

| 20.2.1           | Setting of the sleep mode                                                              | 628 |

| 20.2.2           | Release of sleep mode                                                                  | 631 |

|                  | p sleep mode                                                                           |     |

| 20.3.1           | The setting for deep sleep mode                                                        |     |

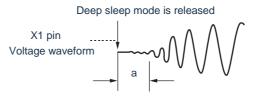

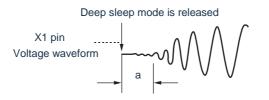

| 20.3.2           | Release of deep sleep mode                                                             | 634 |

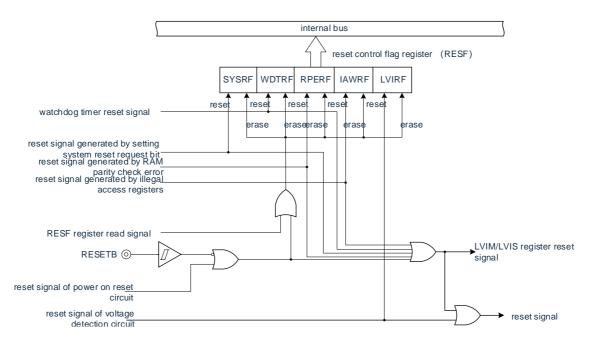

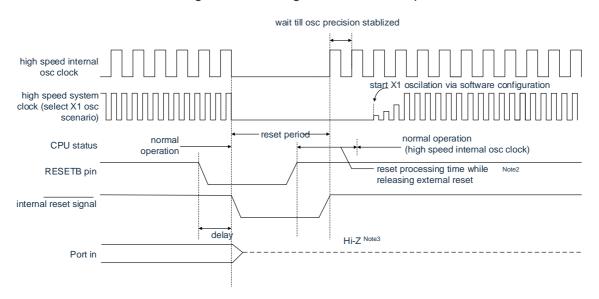

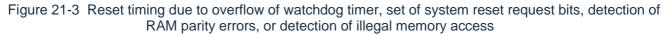

| Chapter 27       | Reset Function                                                                         | 636 |

| •                | ister for confirming the reset source                                                  |     |

| 21.1.1           | Reset control flag register (RESF)                                                     | 641 |

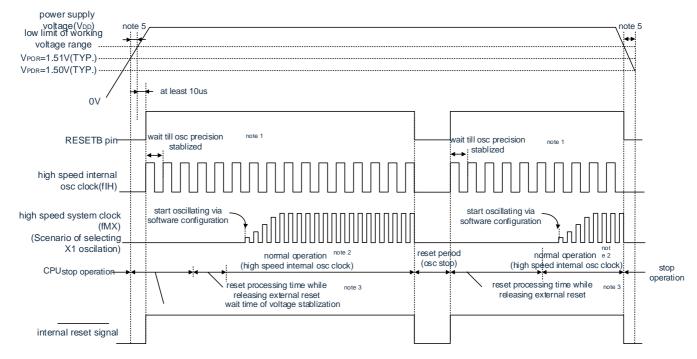

| Chapter 22       | 2 Power-On Reset Circuit                                                               | 644 |

| 22.1 Fun         | ction of power-on reset circuit                                                        | 644 |

| 22.2 Stru  | cture of power-on reset circuit                                     | 645 |

|------------|---------------------------------------------------------------------|-----|

| 22.3 Ope   | ration of power-on reset circuit                                    | 645 |

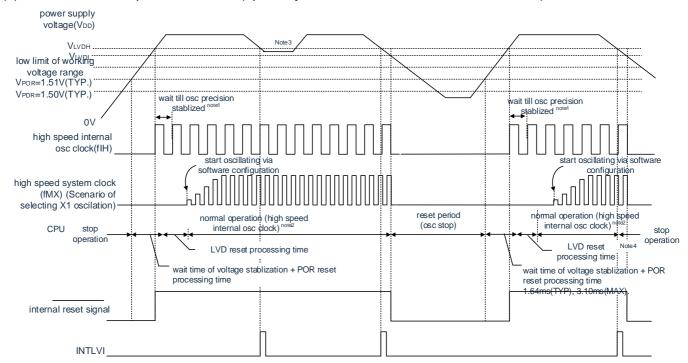

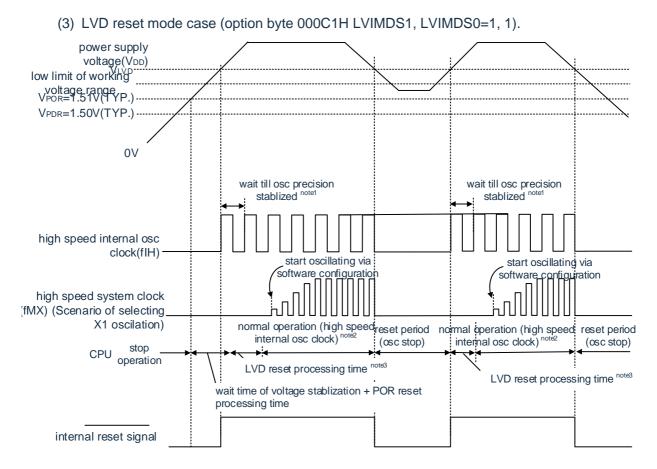

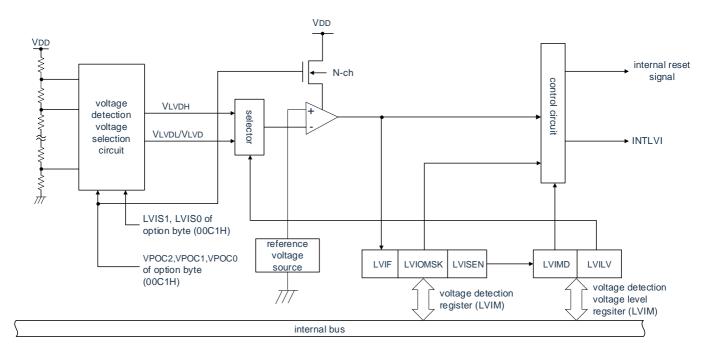

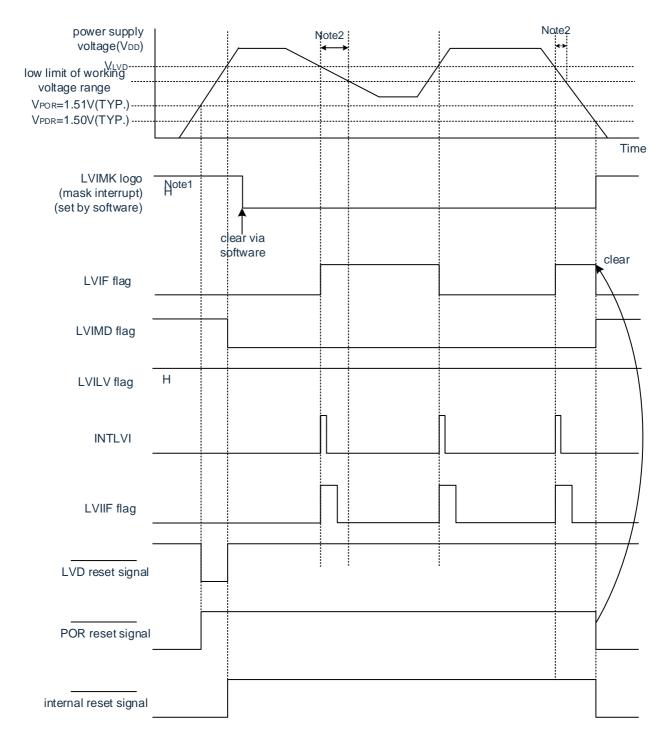

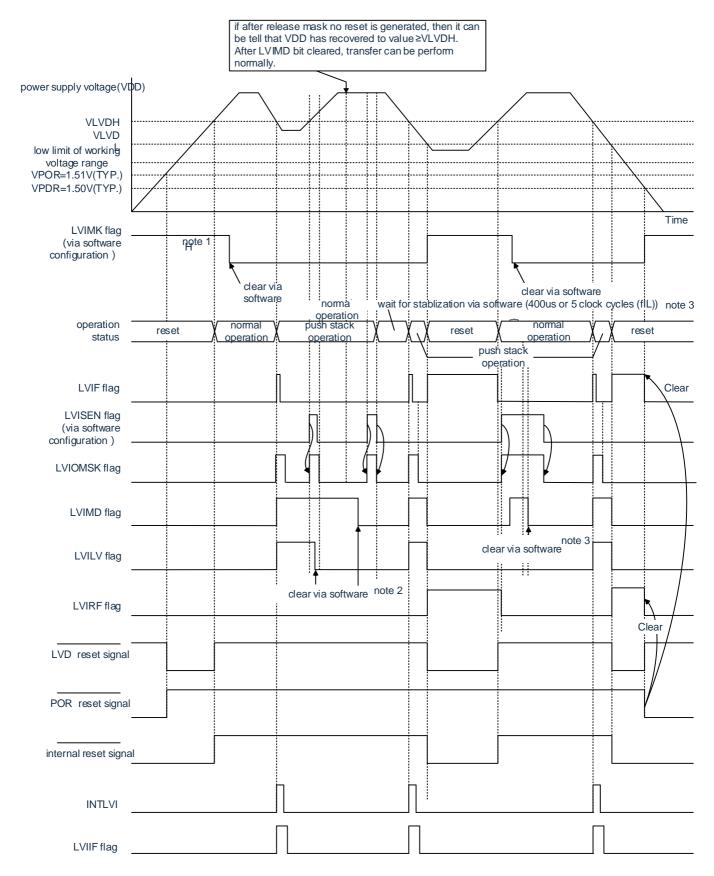

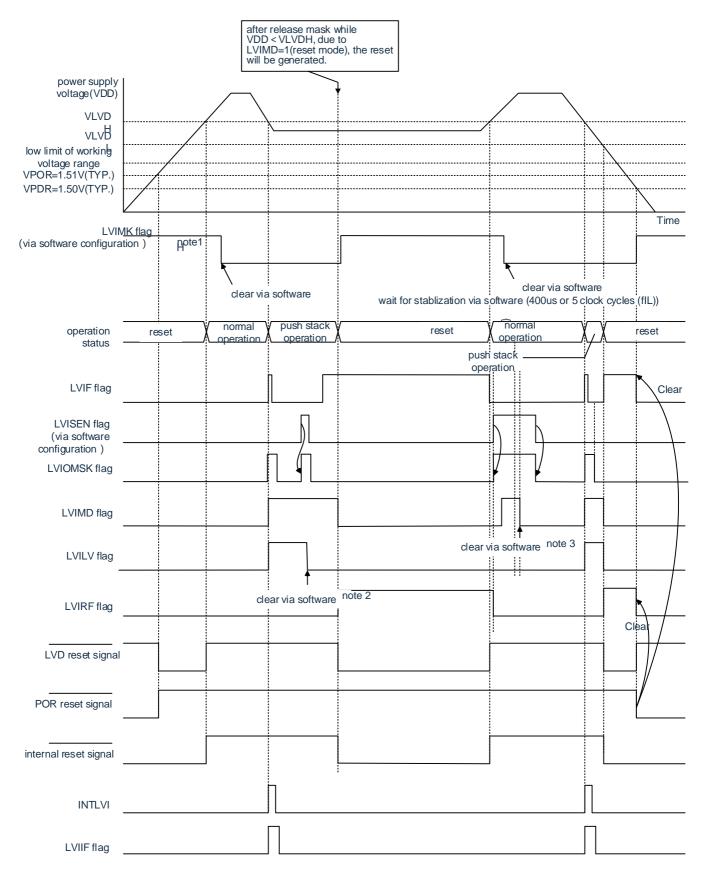

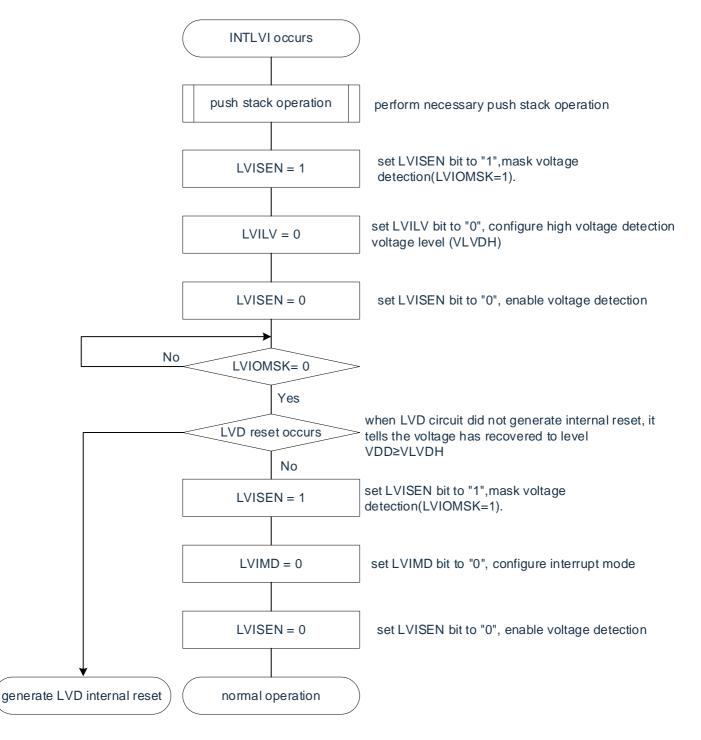

| Chapter 23 | 3 Voltage Detection Circuit                                         | 649 |

| 23.1 Fun   | ction of voltage detection circuit                                  | 649 |

| 23.2 Stru  | cture of voltage detection circuit                                  | 650 |

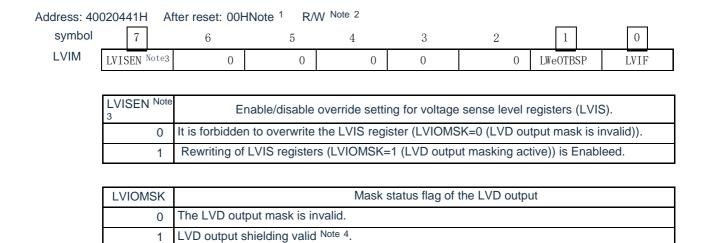

| 23.3 Reg   | isters for controlling voltage detection circuit                    | 651 |

| 23.3.1     | Voltage sense register (LVIM).                                      |     |

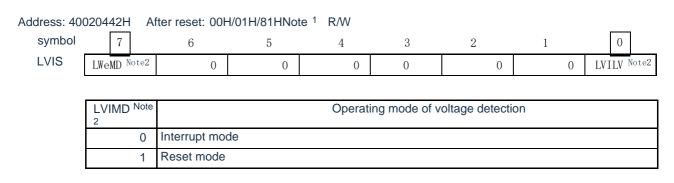

| 23.3.2     | Voltage sense level register (LVIS)                                 |     |

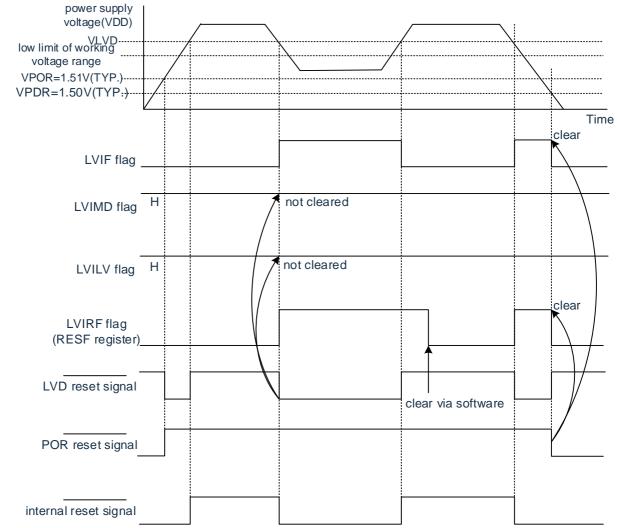

|            | ration of voltage detection circuit                                 |     |

| 23.4.1     | Settings when used in reset mode                                    |     |

| 23.4.2     | Settings when used in interrupt mode                                |     |

| 23.4.3     | Settings for interrupt & reset mode                                 |     |

| 23.5 Con   | siderations for voltage detection circuits                          |     |

| Chapter 24 | Security Features                                                   |     |

| 24.1 Ove   | rview                                                               | 667 |

| 24.2 Reg   | isters used by security functions                                   | 668 |

| 24.3 Ope   | ration of security functions                                        | 668 |

| 24.3.1     | Flash CRC operation function (high-speed CRC)                       |     |

| 24.3.2     | CRC operation function (general CRC)                                |     |

| 24.3.3     | RAM parity error detection function                                 |     |

| 24.3.4     | SFR protection function                                             |     |

| 24.3.5     | Frequency detection function                                        |     |

| 24.3.6     | A/D test function                                                   |     |

| 24.3.7     | Digital output signal level detection function for input/output pin |     |

| 24.3.8     | Product unique identification register                              |     |

| Chapter 25 |                                                                     |     |

|            | ction of temperature sensor                                         |     |

|            | ster for temperature sensor                                         |     |

| 25.2.1     | Temperature sensor calibration data register TSN25                  |     |

| 25.2.2     | Temperature sensor calibration data register TSN85                  |     |

|            | uctions for use with the temperature sensor                         |     |

| 25.3.1     | How the temperature sensor is used                                  |     |

| 25.3.2     | How to use the temperature sensor                                   |     |

| Chapter 26 |                                                                     |     |

|            | ction of option byte                                                |     |

| 26.1.1     | User option bytes (000C0H~000C2H)                                   |     |

| 26.1.2     | Flash data protection option bytes (000C3H, 500004H)                |     |

|            | nat of user option byte                                             |     |

| 26.3 Forn  | nat of flash data protection option bytes                           |     |

| Chapter 27 |                                                                     |     |

|            | cription of FLASH control                                           |     |

|            | cture of FLASH memory                                               |     |

| -          | isters for controlling FLASH                                        |     |

| 27.3.1     | Flash write protection register (FLPROT)                            |     |

| 27.3.2     | FLASH operation control registers (FLOPMD1, FLOPMD2)                |     |

#### CMS32L051 User Manual |Chapter 1 CPU

| 27.3.3    | Flash erase control register (FLERMD)                  | 697 |

|-----------|--------------------------------------------------------|-----|

| 27.3.4    | Flash status register (FLSTS)                          | 698 |

| 27.3.5    | Flash full-chip erase time control register (FLCERCNT) | 698 |

| 27.3.6    | Flash sector erase time control register (FLSERCNT)    | 699 |

| 27.3.7    | Flash write time control register (FLPROCNT)           | 700 |

| 27.4 FLA  | SH operation method                                    | 701 |

| 27.4.1    | Sector erase                                           | 701 |

| 27.4.2    | Chip erase                                             | 702 |

| 27.4.3    | Programming (word program).                            | 702 |

| 27.5 Flas | h read                                                 | 702 |

| 27.6 Cau  | tions for FLASH operation                              | 702 |

| Appendix  | Revision History                                       | 703 |

### Chapter 1 CPU

#### 1.1 Overview

This section briefly introduces the features and debugging features of the ARM Cortex-M0+ core on this product, please refer to the relevant ARM documentation for details.

#### 1.2 Cortex-M0+ core features

- The ARM Cortex-M0+ processor is a 32-bit RISC core with 2-stage pipeline that only supports privileged mode

- Single -cycle hardware multiplier

- Nested Vector Interrupt Controller (NVIC)

- 1 non-maskable interrupt (NMI)

- Supports 32 maskable interrupt requests (IRQs)

- 4 interrupt priorities

- System Timer (SysTick) is a 24-bit countdown timer with a choice of f<sub>CLK</sub> or f<sub>IL</sub> counting clock

- Vector Table Offset Register (VTOR)

- The software can write VTOR to relocate the vector table start address to a different location

- The default value of this register is 0x0000\_0000, the low 8 bits are ignored for writes, and read to zero, which means that the offset is 256 bytes aligned.

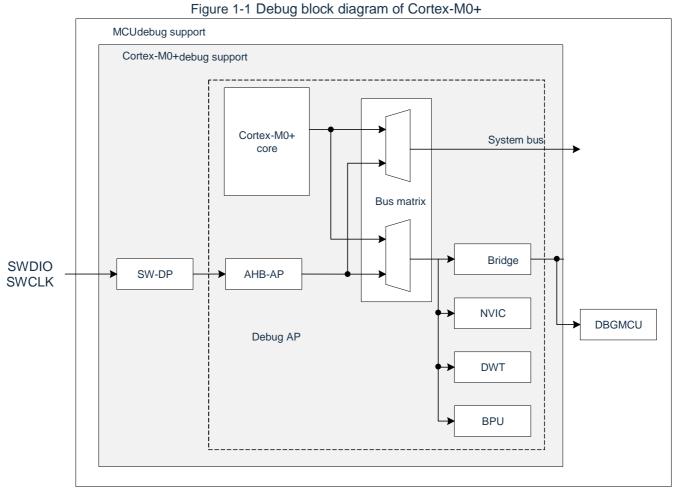

#### 1.3 Debugging features

- 2-wire SWD debug interface

- Supports pause, resume, and stepping through programs

- Access the processor's core registers and special function registers

- 4 hardware breakpoints (BPUs).

- Unlimited software breakpoints (BKPT instructions).

- 2 Data observation points (DWTs).

- Memory is accessed while the kernel is executing.

Note: SWD does not work in deep sleep mode, please debug in active and sleep modes.

#### 1.4 SWD interface pin

The two GPIOs of this product can be used as SWD interface pins, which are present in all packages.

| SWD port name | Debugging capabilities   | Pin assignment |

|---------------|--------------------------|----------------|

| SWCLK         | Serial clock             | P137           |

| SWDIO         | Serial data input/output | P40            |

#### Table 1-1 SWD debug port pins

When the SWD function is not used, SWD can be disabled by setting the debug **S**top control register (DBGSTOPCR).

| Bit No.       | 31 | 30 | 29 | 28 | 27 | 26 | 25     | 24     |

|---------------|----|----|----|----|----|----|--------|--------|

| DBGSTOPCR     | -  | -  | -  | -  | -  | -  | -      | SWDIS  |

| default value | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      |

|               |    |    |    |    |    |    |        |        |

| Bit No.       | 23 | 22 | 21 | 20 | 19 | 18 | 17     | 16     |

| DBGSTOPCR     | -  | -  | -  | -  | -  | -  | -      | -      |

| default value | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      |

|               |    |    |    |    |    |    |        |        |

| Bit No.       | 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8      |

| DBGSTOPCR     | -  | -  | -  | -  | -  | -  | -      | -      |

| default value | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      |

|               |    |    |    |    |    |    |        |        |

| Bit No.       | 7  | 6  | 5  | 4  | 3  | 2  | 1      | 0      |

| DBGSTOPCR     | -  | -  | -  | -  | -  | -  | FRZEN1 | FRZEN0 |

| default value | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0      |

| SWDIS | SWD debug interface status                                                                    |

|-------|-----------------------------------------------------------------------------------------------|

|       | The SWD debug interface is enabled. P40 cannot be used as a GPIO when the debugger is         |

| 0     | connected (because the ENO and DOUT of the IOBUF are controlled by the debugger at this time) |

| 1     | The SWD debug interface is disabled. The P40 can be used as a GPIO                            |

|      | n the state where the debugger is connected and the CPU is in the debug state (HALTED=1), the imer is peripheral module action/stop Note 1 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0 Pe | Peripheral actions                                                                                                                         |

| 1 Pe | Peripheral stops                                                                                                                           |

| FRZEN1 | In the state where the debugger is connected and the CPU is in the debug state (HALTED=1), the communication system peripheral module action/stop Note 2 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Peripheral actions                                                                                                                                       |

| 1      | Peripheral stops                                                                                                                                         |

Note 1: The timer peripheral modules of this product include: Timer4, a universal timer unit.

Note 2: The peripheral modules of the communication system of this product include: communication serial communication unit, serial IICA.

#### 1.5 ARM reference document

The built-in debugging features in the Cortex®-M0+ kernel is part of the ARM® CoreSight design suite. For related documents, please refer to:

- Cortex-M0®+ Technical Reference Manual (TRM)

- ARM® debug interface V5

- ARM® CoreSight Design Kit Version r1p1 Technical Reference Manual

- ARM® CoreSight™ MTB-M0+ Technical Reference Manual

### Chapter 2 Pin Function

#### 2.1 Port function

Refer to the data sheets for each product family.

#### 2.2 Port multiplexing function

Refer to the data sheets for each product family.

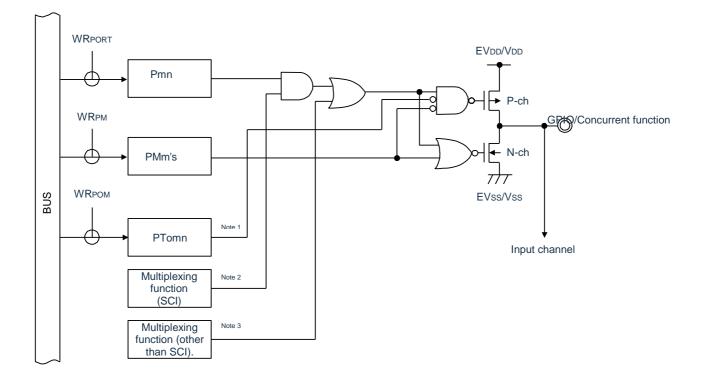

2.3 Registers for controlling port functions

The port function is controlled through the following registers.

- Port Mode Register (PMxx)

- Port Register (Pxx)

- Pull-Up Resistor Selection Register (PUxx)

- Pull-Down Resistor Selection Register (PDxx)

- Port Output Mode Register (POMx)

- Port Mode Control Register (PMCxx)

- Port Set Control Register (PSETxx)

- Port Clear Control Register (PCLRxx)

- Port Output Multiplexing Function Configuration Register (PxxCFG).

- Port Input Multiplexing Function Configuration Register (TI10PCFG, TI11PCFG, TI12PCFG, TI13PCFG, INTP0PCFG, INTP1PCFG, INTP2PCFG, INTP3PCFG, SDI00PCFG, SCLKI00PCFG, SS00PCFG, SDI20PCFG, SCLKI20PCFG, SDAA0PCFG, SCLA0PCFG, RXD1PCFG).

- SPI Port Multiplexing Configuration Register (SPIPCFG)

Note: Assigned registers and bits vary from product to product. For the registers and bits assigned by each product, refer to Table 2-1. The initial value must be set for the unassigned bits.

|         |   |                  |                 |                    | Bit                | name             |                  |                   |                   |            |            |            |            |            |

|---------|---|------------------|-----------------|--------------------|--------------------|------------------|------------------|-------------------|-------------------|------------|------------|------------|------------|------------|

| port    |   | PMxx<br>register | Pxx<br>register | PSETxx<br>register | PCLRxx<br>register | PUxx<br>register | PDxx<br>register | POMxx<br>register | PMCxx<br>register | 48<br>Pins | 40<br>Pins | 32<br>Pins | 24<br>Pins | 20<br>Pins |

| Dert 0  | 0 | PM00             | P00             | PSET00             | PCLR00             | PU00             | PD00             | POM00             | PMC00             | 0          | 0          | 0          | _          | _          |

| Port 0  | 1 | PM01             | P01             | PSET01             | PCLR01             | PU01             | PD01             | POM01             | PMC01             | 0          | 0          | 0          |            | _          |

|         | 0 | PM10             | P10             | PSET10             | PCLR10             | PU10             | PD10             | POM10             | PMC10             | 0          | 0          | 0          | 0          | 0          |

|         | 1 | PM11             | P11             | PSET11             | PCLR11             | PU11             | PD11             | POM11             | PMC11             | 0          | 0          | 0          | 0          | 0          |

|         | 2 | PM12             | P12             | PSET12             | PCLR12             | PU12             | PD12             | POM12             | PMC12             | 0          | 0          | 0          | 0          | 0          |

| Dort 1  | 3 | PM13             | P13             | PSET13             | PCLR13             | PU13             | PD13             | POM13             | PMC13             | 0          | 0          | 0          | 0          | 0          |

| Port 1  | 4 | PM14             | P14             | PSET14             | PCLR14             | PU14             | PD14             | POM14             | PMC14             | 0          | 0          | 0          | 0          | 0          |

|         | 5 | PM15             | P15             | PSET15             | PCLR15             | PU15             | PD15             | POM15             | PMC15             | 0          | 0          | 0          | 0          | _          |

|         | 6 | PM16             | P16             | PSET16             | PCLR16             | PU16             | PD16             | POM16             | PMC16             | 0          | 0          | 0          |            | _          |

|         | 7 | PM17             | P17             | PSET17             | PCLR17             | PU17             | PD17             | POM17             | PMC17             | 0          | 0          | 0          |            | _          |

|         | 0 | PM20             | P20             | PSET20             | PCLR20             | PU20             | PD20             | POM20             | PMC20             | 0          | 0          | 0          | 0          | 0          |

|         | 1 | PM21             | P21             | PSET21             | PCLR21             | PU21             | PD21             | POM21             | PMC21             | 0          | 0          | 0          | 0          | 0          |

|         | 2 | PM22             | P22             | PSET22             | PCLR22             | PU22             | PD22             | POM22             | PMC22             | 0          | 0          | 0          | 0          | 0          |

| Port 2  | 3 | PM23             | P23             | PSET23             | PCLR23             | PU23             | PD23             | POM23             | PMC23             | 0          | 0          | 0          | 0          | 0          |

| r'uii Z | 4 | PM24             | P24             | PSET24             | PCLR24             | PU24             | PD24             | POM24             | PMC24             | 0          | 0          | _          | 0          | _          |

|         | 5 | PM25             | P25             | PSET25             | PCLR25             | PU25             | PD25             | POM25             | PMC25             | 0          | 0          | _          | _          | _          |

|         | 6 | PM26             | P26             | PSET26             | PCLR26             | PU26             | PD26             | POM26             | PMC26             | 0          |            | _          | _          | _          |

|         | 7 | PM27             | P27             | PSET27             | PCLR27             | PU27             | PD27             | POM27             | PMC27             | 0          | _          | —          | _          | _          |

Table 2-1Registers assigned to each product PMxx, Pxx, PSETxx, PCLRxx, PUxx, PDxx, POMxx,<br/>PMCxx and their bits (1/2)

Note 1.(-A) is limited to CMS32L051xx-A series products.

Table 2-1 Registers assigned to each product PMxx, Pxx, PSETxx, PCLRxx, PUxx, PDxx, POMxx, PMCxx and their bits (2/2)

|         |        |                  |                     |                    |                    | Bit nam               | е                     |                         |                   |            |            |            |            |            |

|---------|--------|------------------|---------------------|--------------------|--------------------|-----------------------|-----------------------|-------------------------|-------------------|------------|------------|------------|------------|------------|

| port    |        | PMxx<br>register | Pxx<br>registe<br>r | PSETxx<br>register | PCLRxx<br>register | PUxx<br>register      | PDxx<br>register      | POMxx<br>register       | PMCxx<br>register | 48<br>Pins | 40<br>Pins | 32<br>Pins | 24<br>Pins | 20<br>Pins |

| Port 3  | 0      | PM30             | P30                 | PSET30             | PCLR30             | PU30                  | PD30                  | POM30                   | PMC30             | 0          | 0          | 0          | _          | _          |

| Port 3  | 1      | PM31             | P31                 | PSET31             | PCLR31             | PU31                  | PD30                  | POM31                   | PMC31             | 0          | 0          | 0          | _          | _          |

| Port 4  | 0      | PM40             | P40                 | PSET40             | PCLR40             | PU40                  | _                     | POM40                   | _                 | 0          | 0          | 0          | 0          | 0          |

| FUIL 4  | 1      | PM41             | P41                 | PSET41             | PCLR41             | PU41                  |                       | POM41                   |                   | 0          | —          |            | _          | —          |

| Dort 5  | Port 5 | PM50             | P50                 | PSET50             | PCLR50             | PU50                  | PD50                  | POM50                   | PMC50             | 0          | 0          | 0          |            | —          |

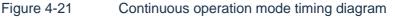

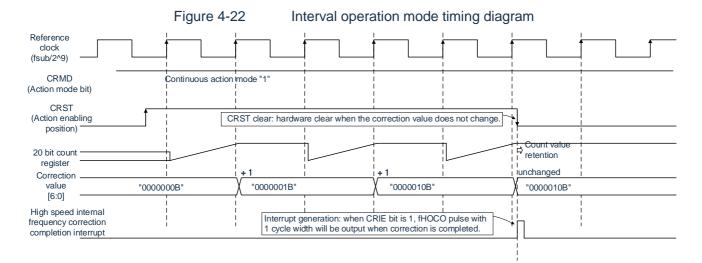

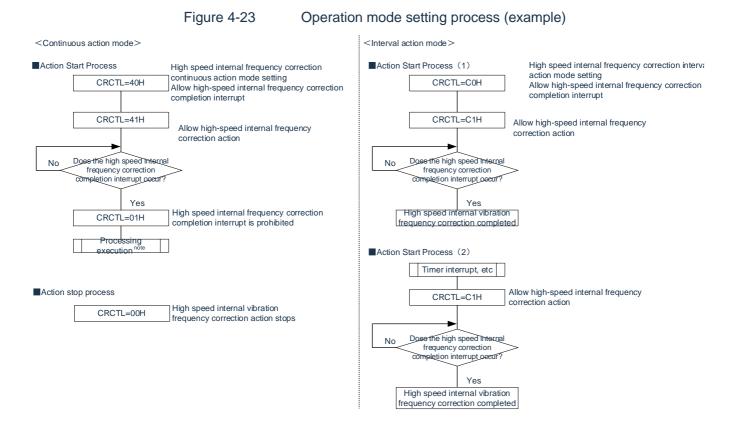

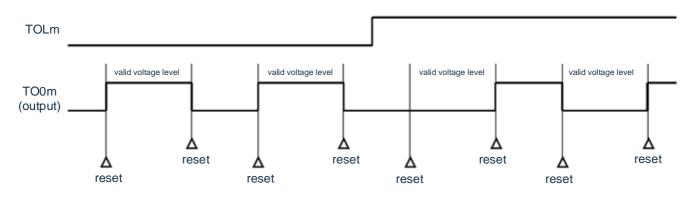

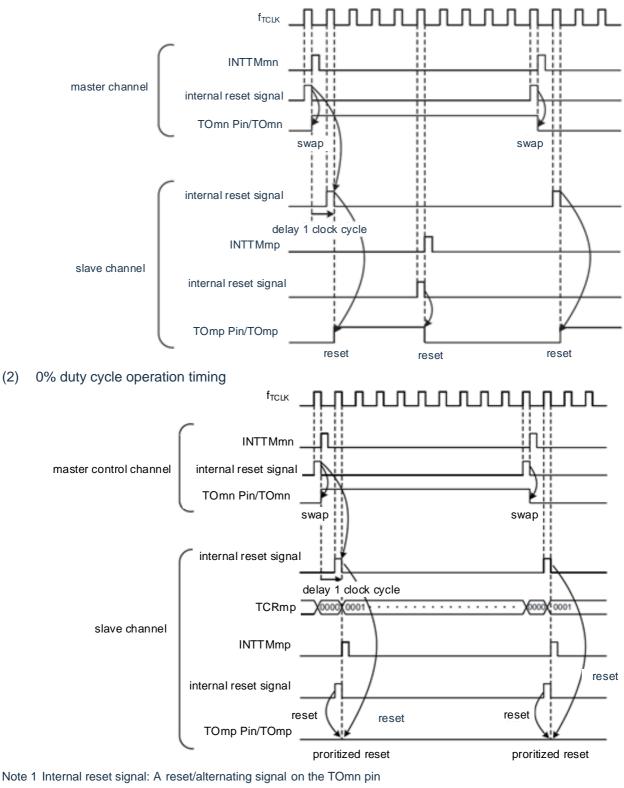

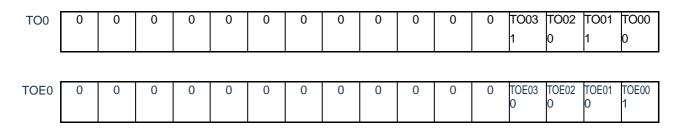

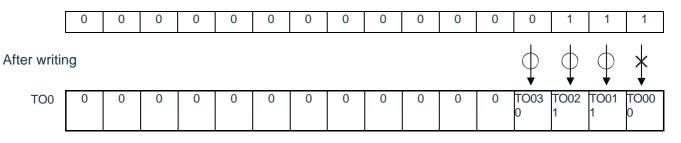

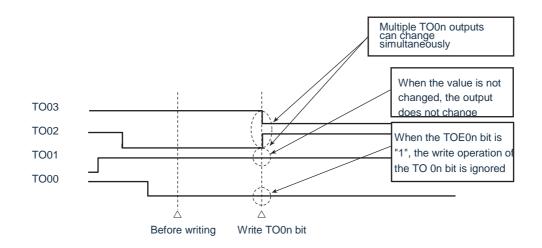

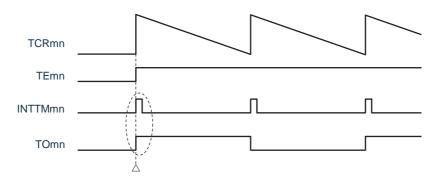

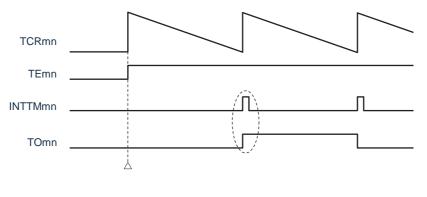

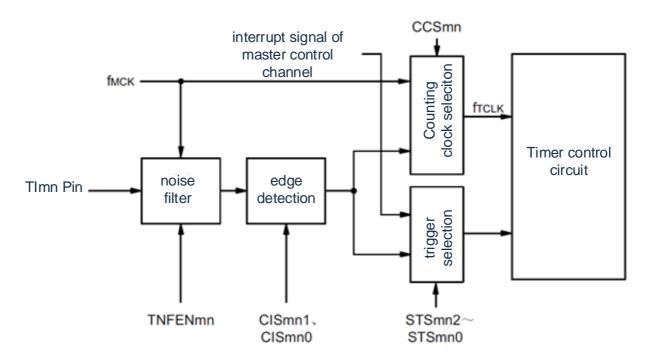

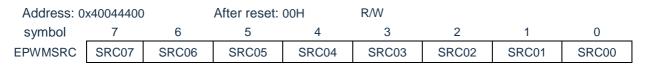

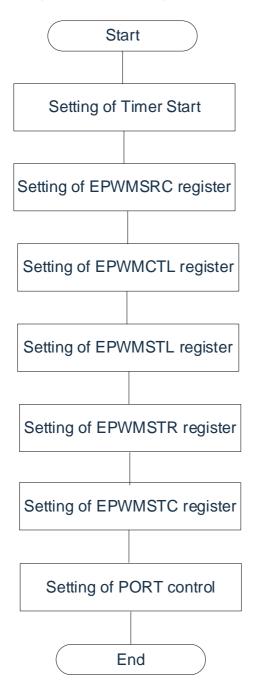

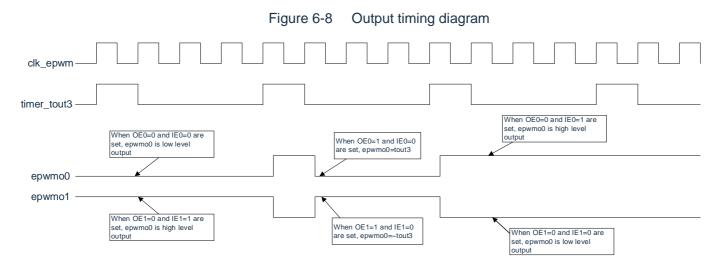

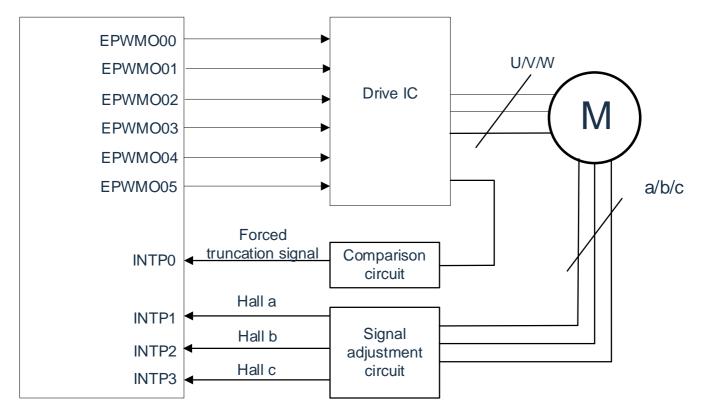

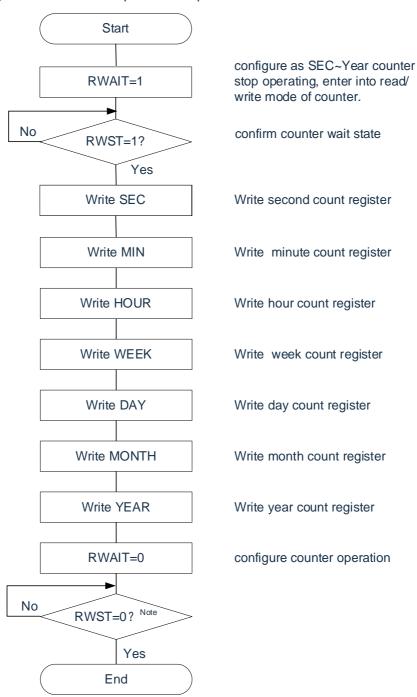

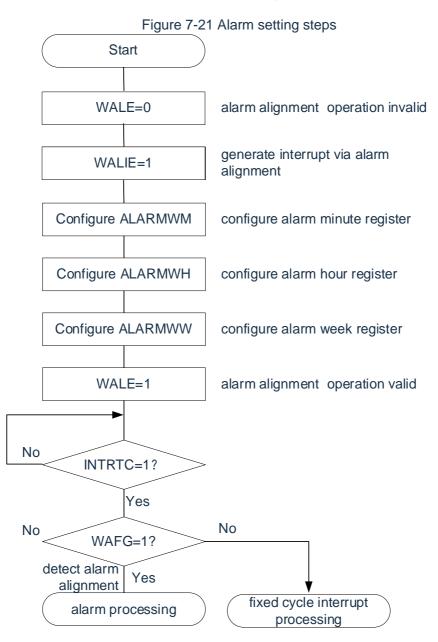

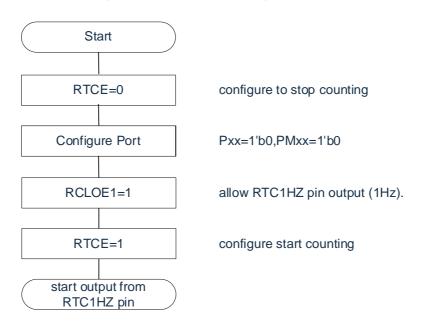

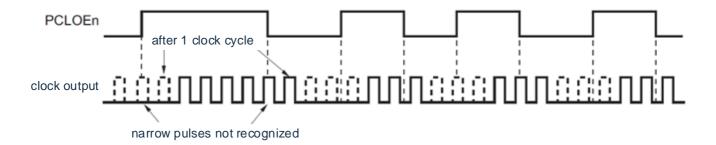

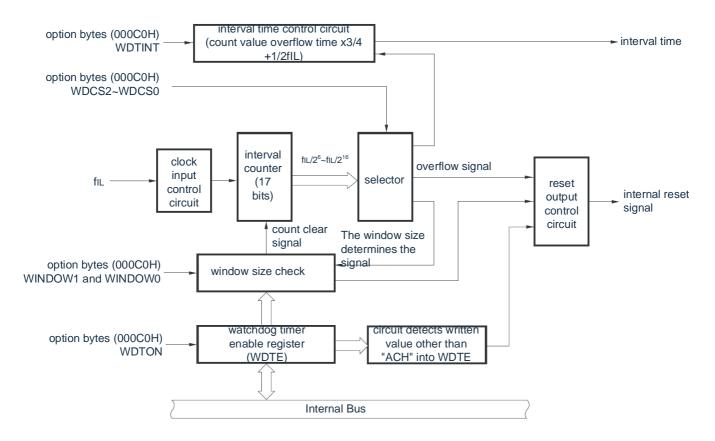

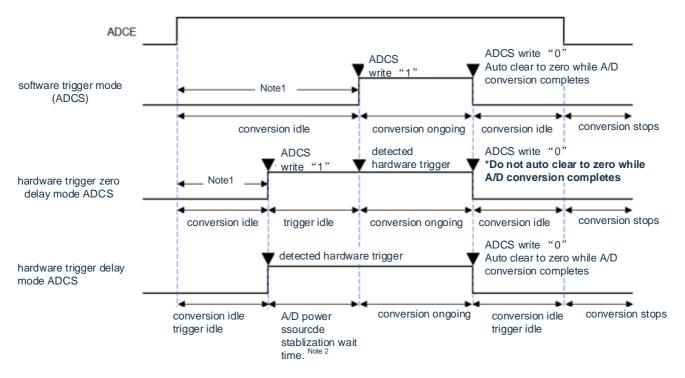

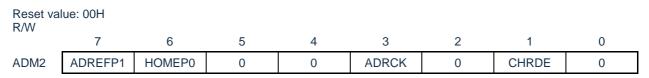

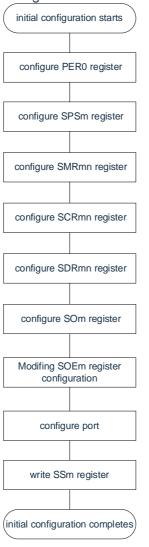

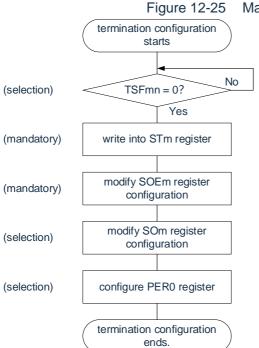

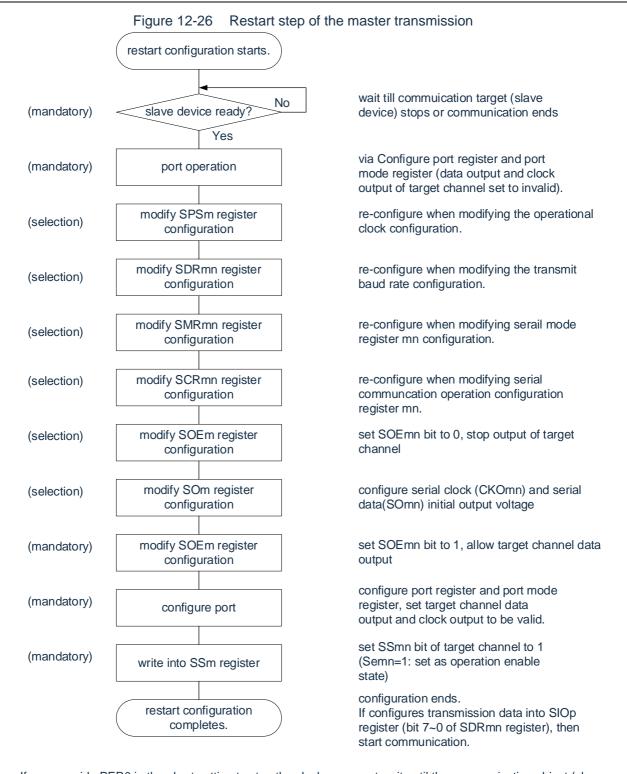

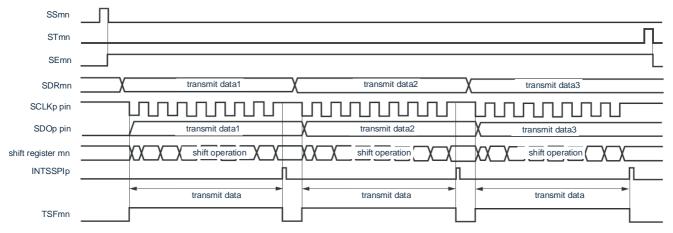

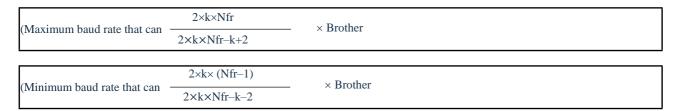

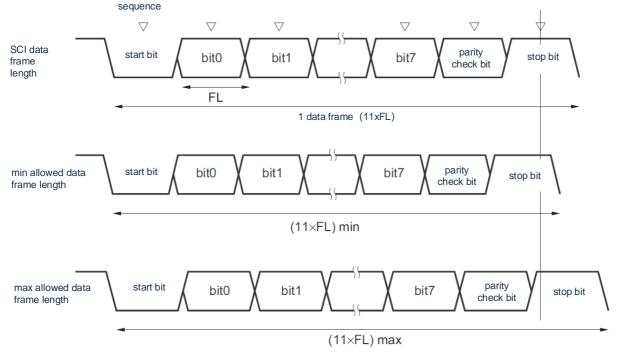

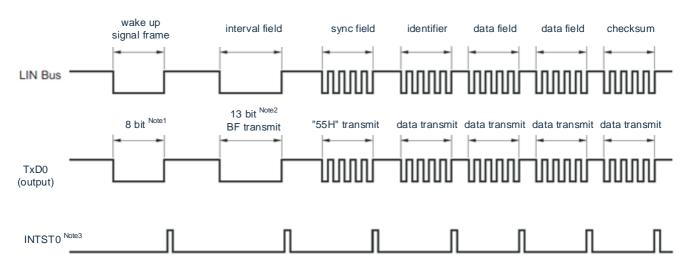

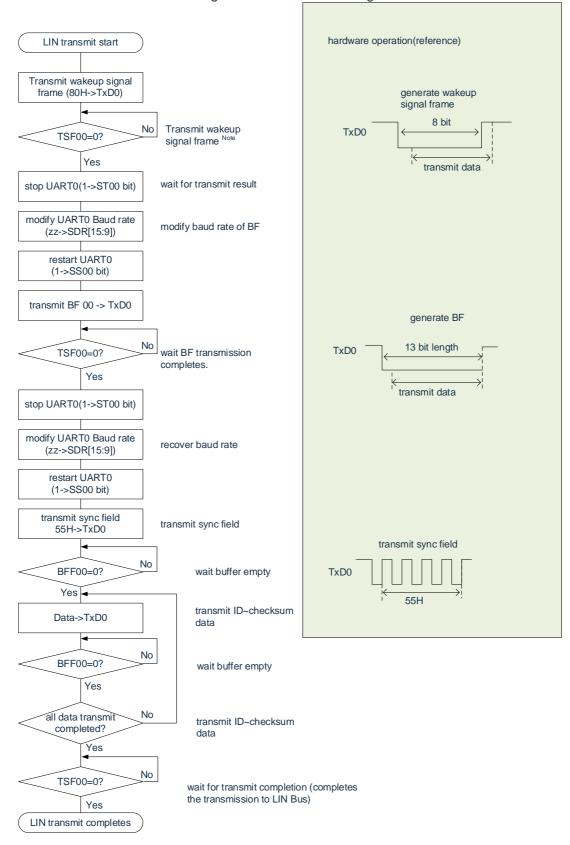

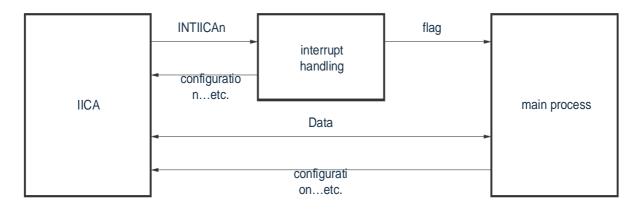

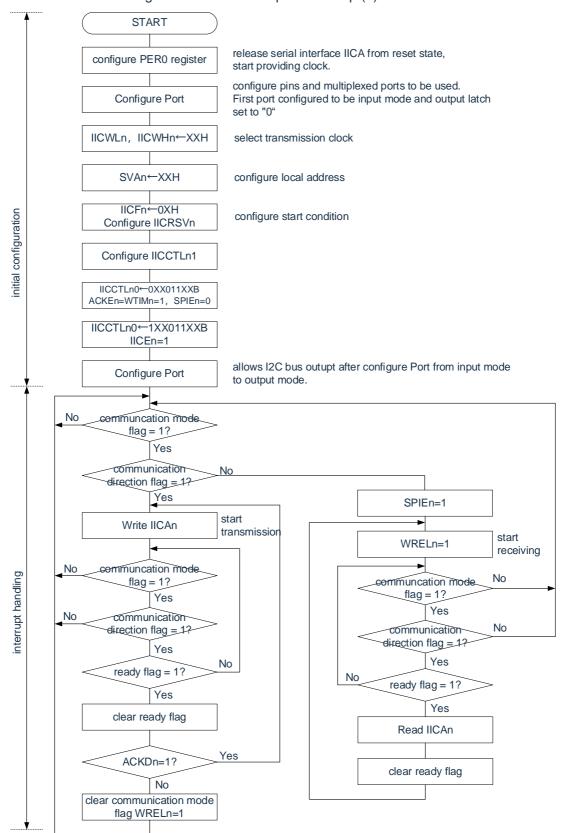

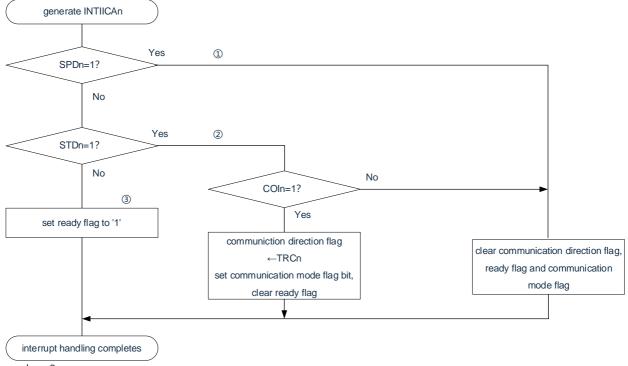

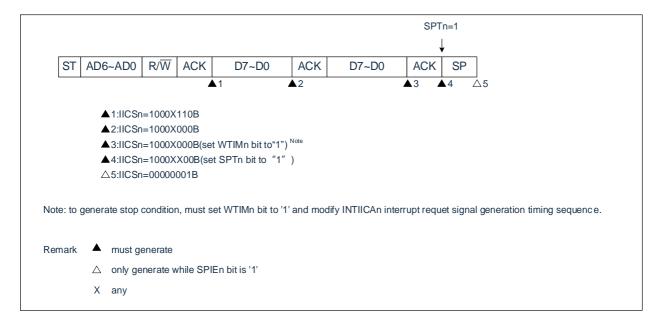

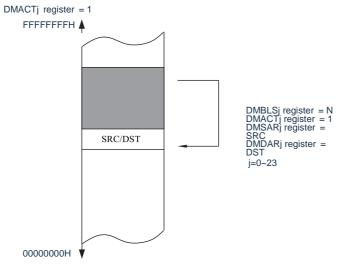

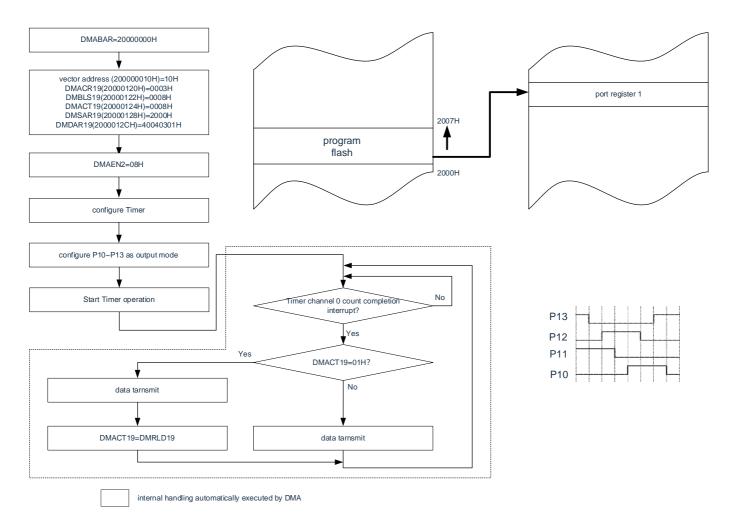

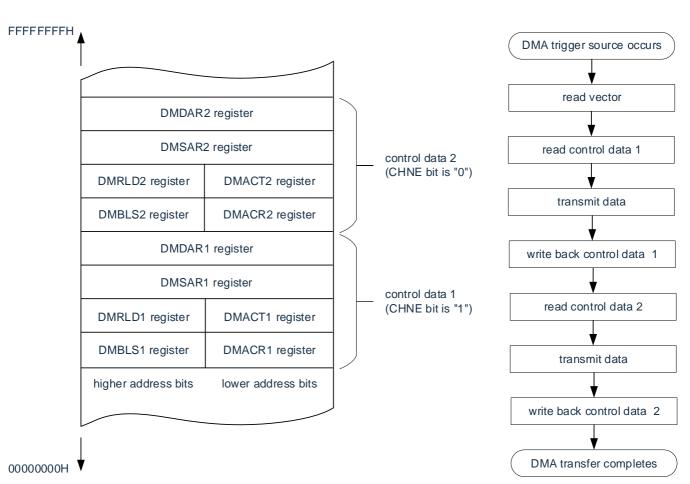

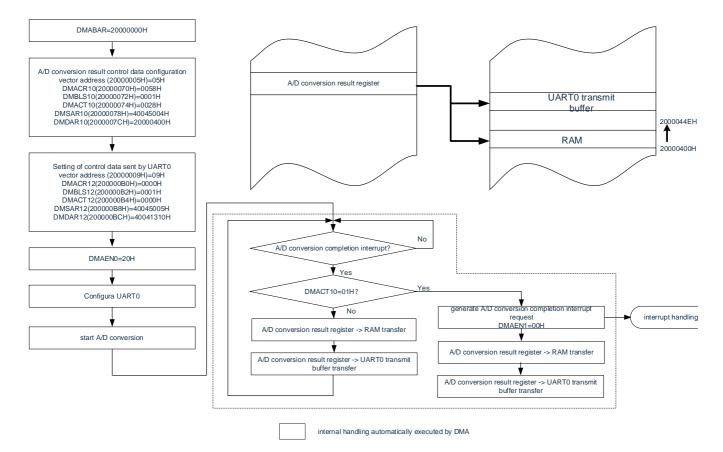

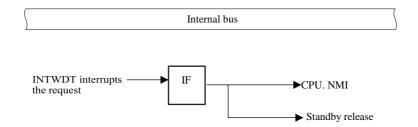

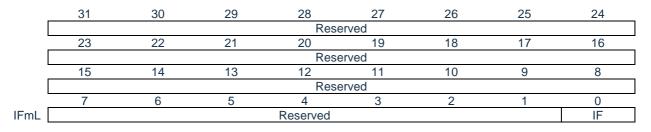

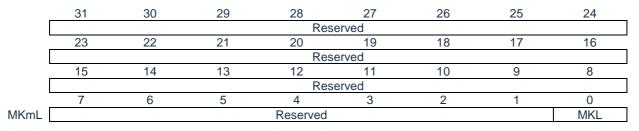

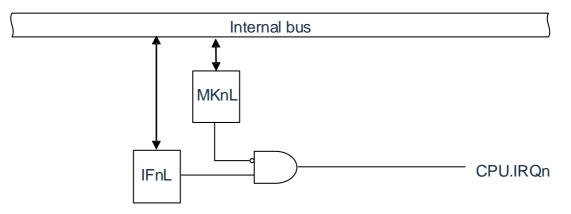

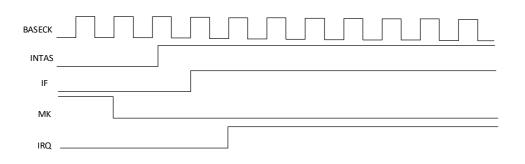

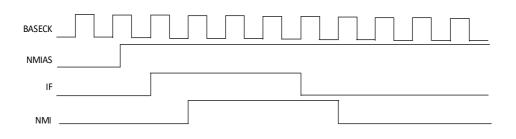

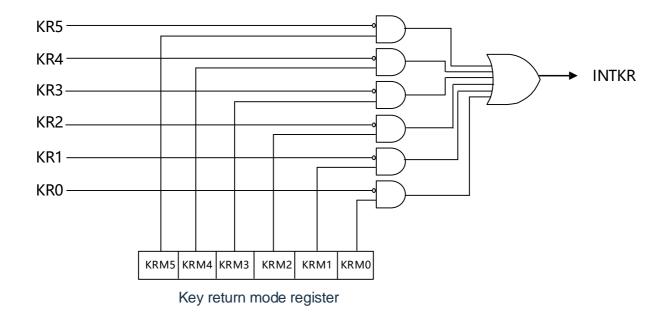

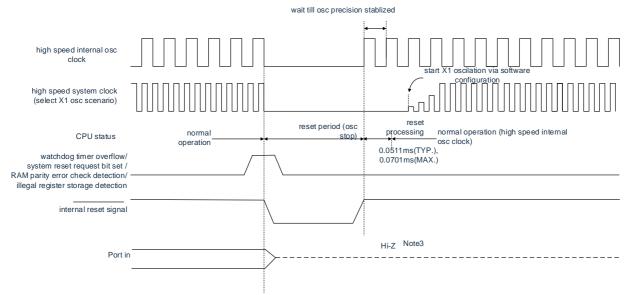

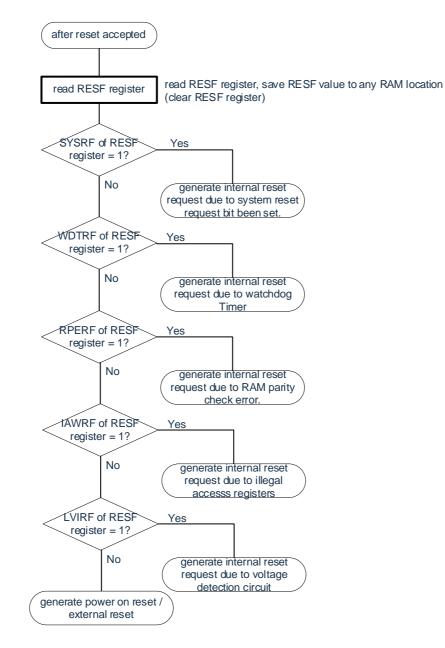

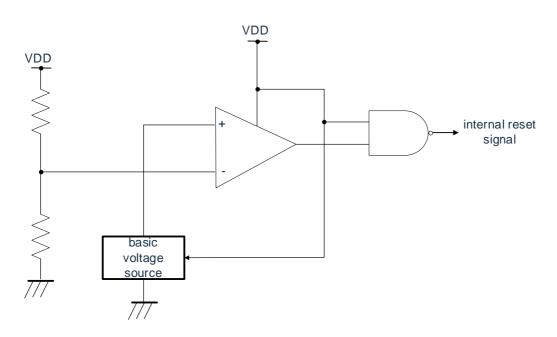

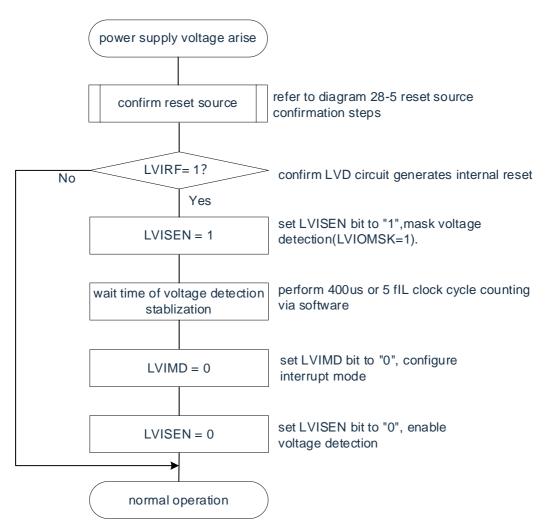

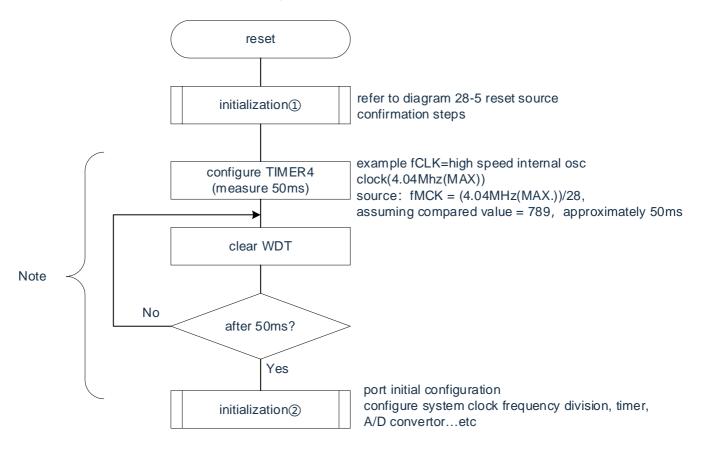

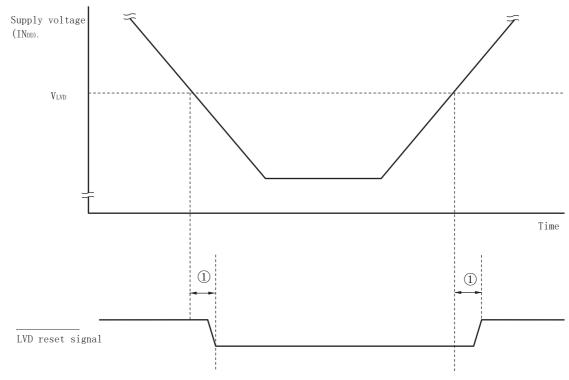

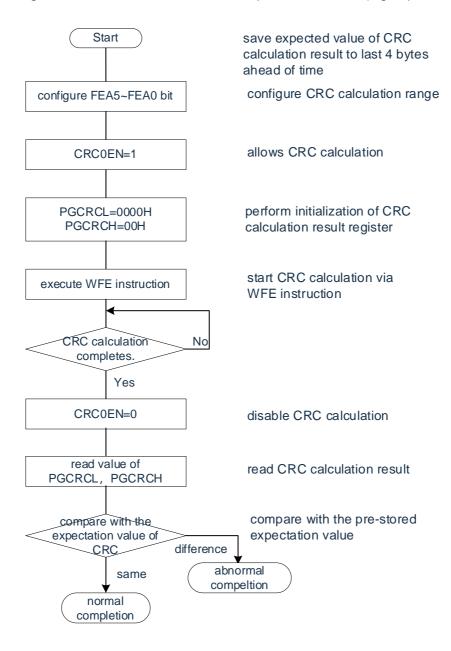

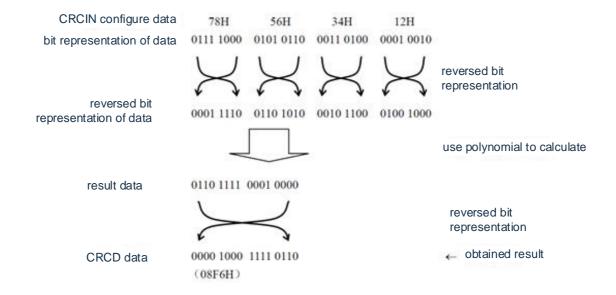

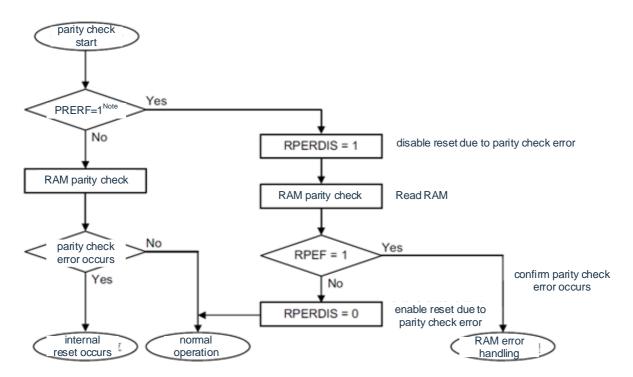

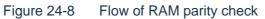

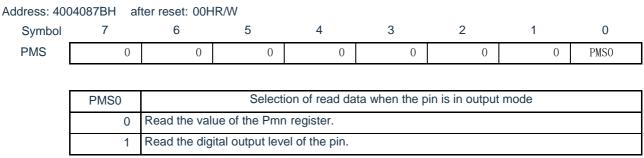

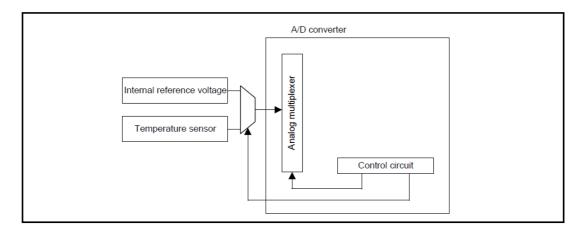

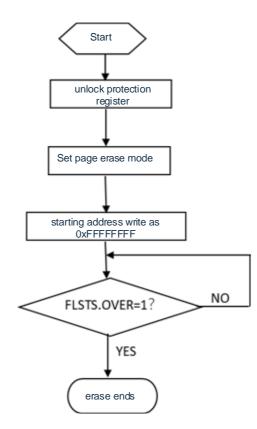

| Ponts   | 1      | PM51             | P51                 | PSET51             | PCLR51             | PU51                  | PD51                  | POM51                   | PMC51             | 0          | 0          | 0          | _          | —          |